一、简介

关于VbyOne接口,V-by-One HS是由日本赛恩电子公司(THine Electornics)开发的适用于平板显示器的信号传输接口标准。目前,广泛应用在多功能打印机等办公设备、车载娱乐设备、机器人、安防系统等领域。

1、较与LVDS的优势

①高速(支持最高4Gbps速率,有效数据速率达3.2Gbps)②低功耗(与固定的速率传输相比,传输速率可变)③低EMI(支持扰码和数据时钟恢复)④支持时钟对齐(时钟信号恢复技术,解决了在LVDS方案下日趋显著化的配线时滞问题)

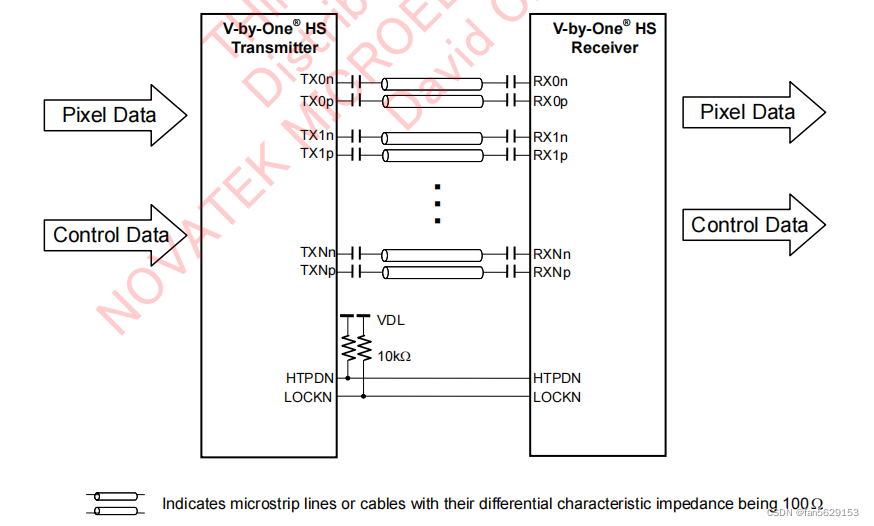

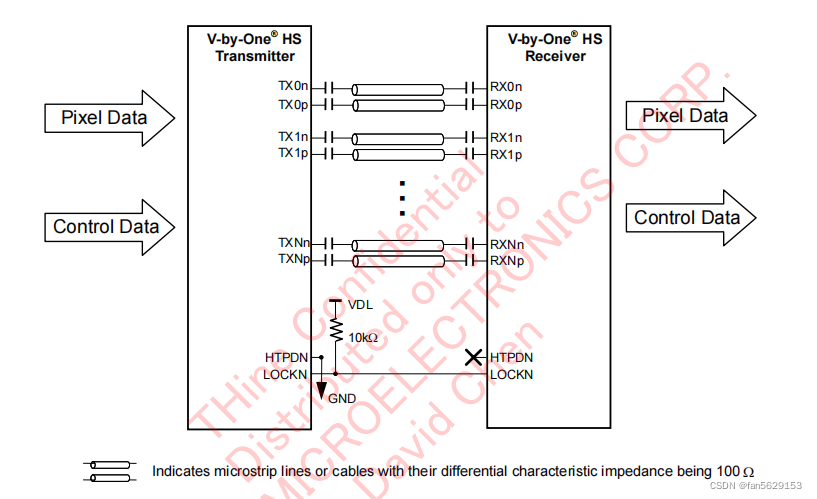

2、V-By-One 系统link框图

①TX和RX数据传输线两端需匹配去耦电容②在TX端控制信号LOCKN,HTPDN需上拉电阻③TX和RX之间传输线数量由色深和pixel clock决定(见table 1)④TX端控制信号有H-sync,V-sync,DE和CTL信号。⑤传输端支持预加重(pre-emphasis),接收端支持EQ均衡(equalizer)

3、data line数量选择

Pixel Clock=H-total*V-total*refresh rate

例:4K*2K 60Hz,Pixel Clock=4400*2250*60=594Mhz

Color depth=R(6、8、10、12bit)+G(6、8、10、12bit)+B(6、8、10、12bit)

①根据Color depth选取数据包字节模式【byte mode】

支持byte mode模式:3byte,4byte,5byte

例:10bit色深,则一个pixel需要3(R,G,B)*10bit=30bit的数据,4byte mode可以支持,另外5byte mode也可以支持。

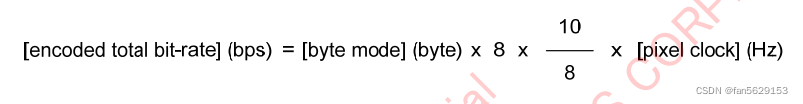

②由于采用8b 10b编码方案,因此物理传输的编码数据量位10位原始数据(只有8位有效数据)。

故编码总bit rate为:

例:4K*2K,60Hz,8bit:encoded total bit rate= 4*8*(10/8)*594M=23.76Gbps

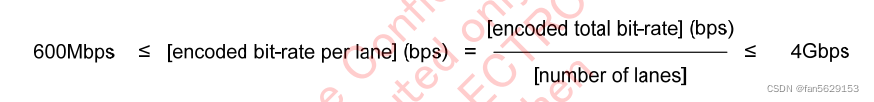

每Line bit rate,lane数通常选择1 2 4 8 16。

例,4K*2K,60Hz,8bit:encoded total per rate=23.76GHz/8=2.97Gbps。符合范围(600Mbps-4Gbps)

4、HTPDN,LOCKN信号作用

HTPDN:确认TX与RX之间的连接状态。在RX未连接时,TX端此信号处于拉高状态;当RX连接好后,RX端将此信号拉低;TX端检测到此信号为低时,开始进入CDR training模式。此信号也可以省略使用,TX端直接拉低。

LOCKN:确认TX,RX之间是否完成CDR training。TX端检测到HTPDN拉L后,TX传输CDR training数据,RX进行CDR training。当完成CDR training后,RX将LOCKN拉L,TX端检测到LOCKN为L状态后,开始ALN training结束后开始传输正常数据。

二、Link Spec

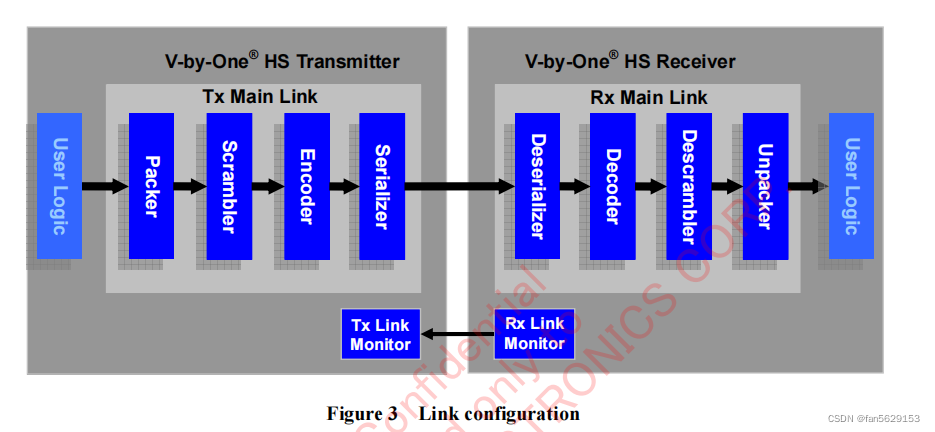

链接连接的建立方法如下。

①Packer:将来自SOC的输入数据被打包到包含8位数据字符的数据包中。

②Scrambler:打包后,在扰码器中使用伪随机数进行乱码。

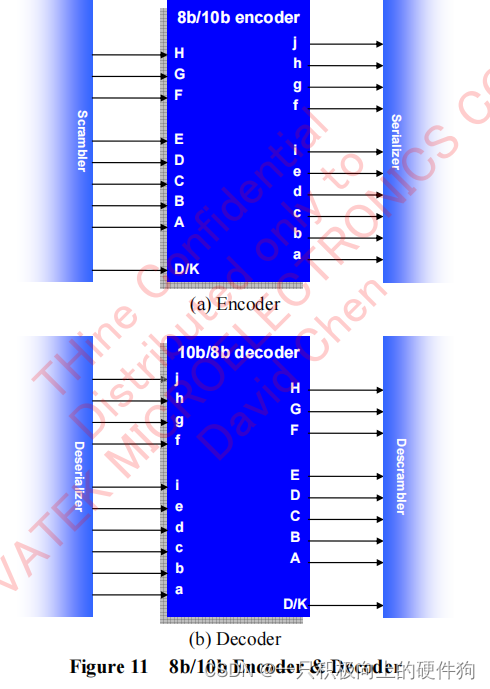

③Encoder:扰码的8位数据包数据被编码为10位字符,以实现近似的DC平衡以及CDR的充分的0-1和1-0转换。

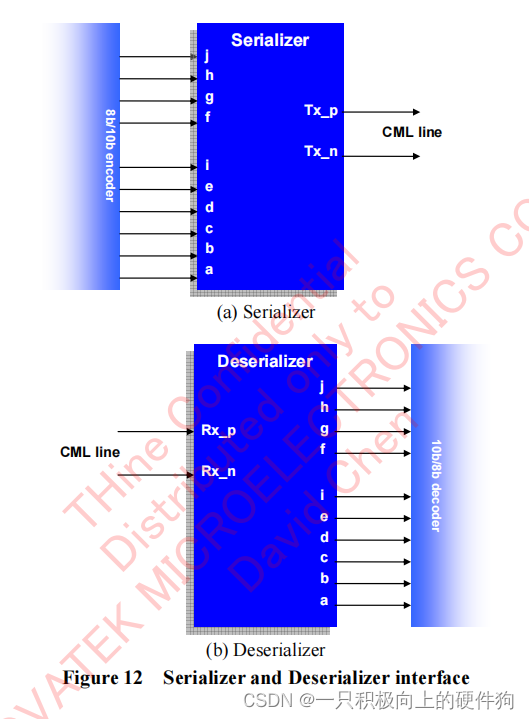

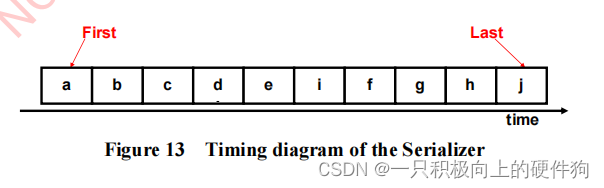

④Serializer:通过序列化器将10位数据字符序列化为1位流。

接收器执行逆过程,以将来自发射器的串行数据转换为用于用户逻辑的像素数据。

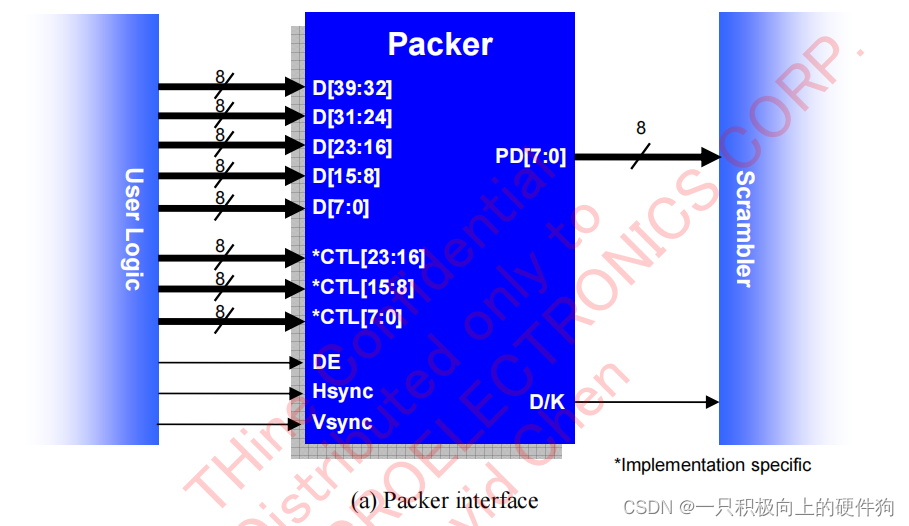

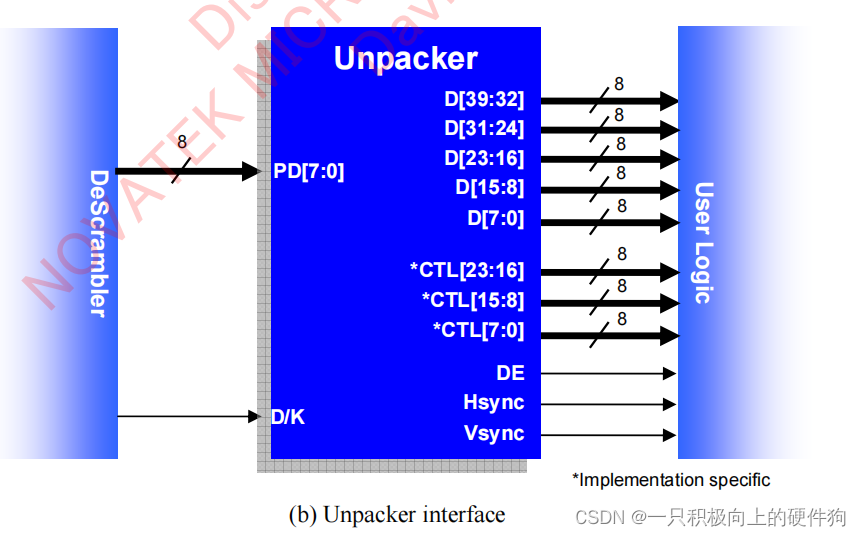

1、Packer and Unpacker

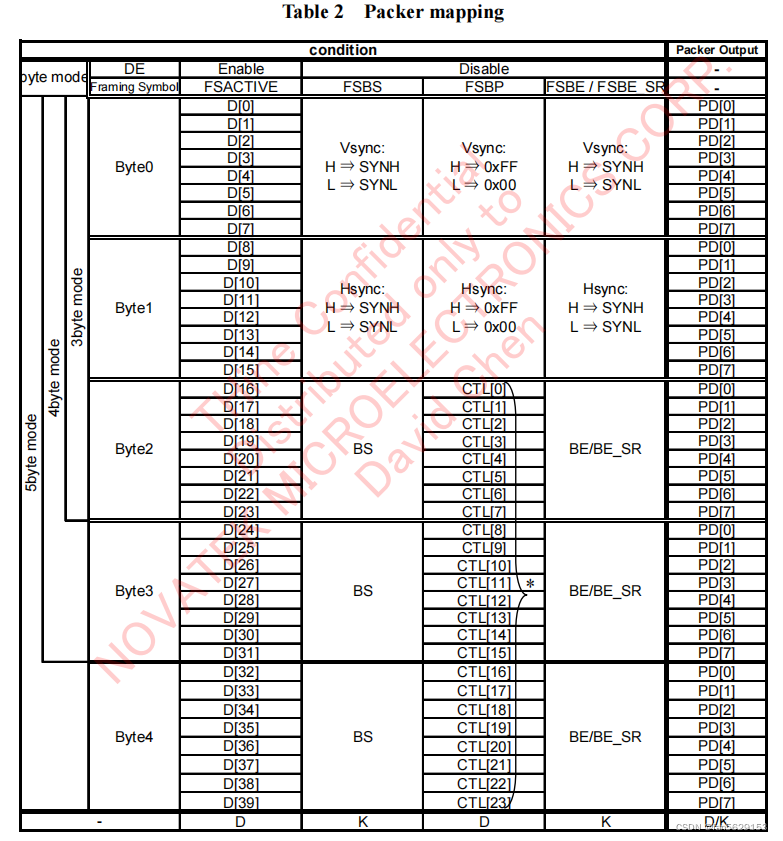

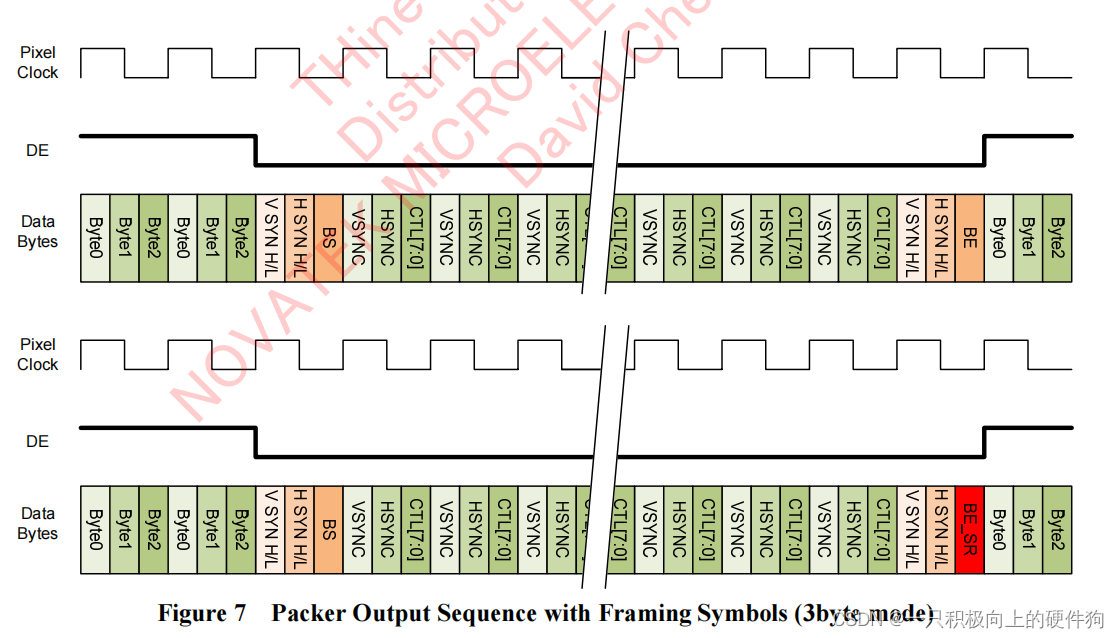

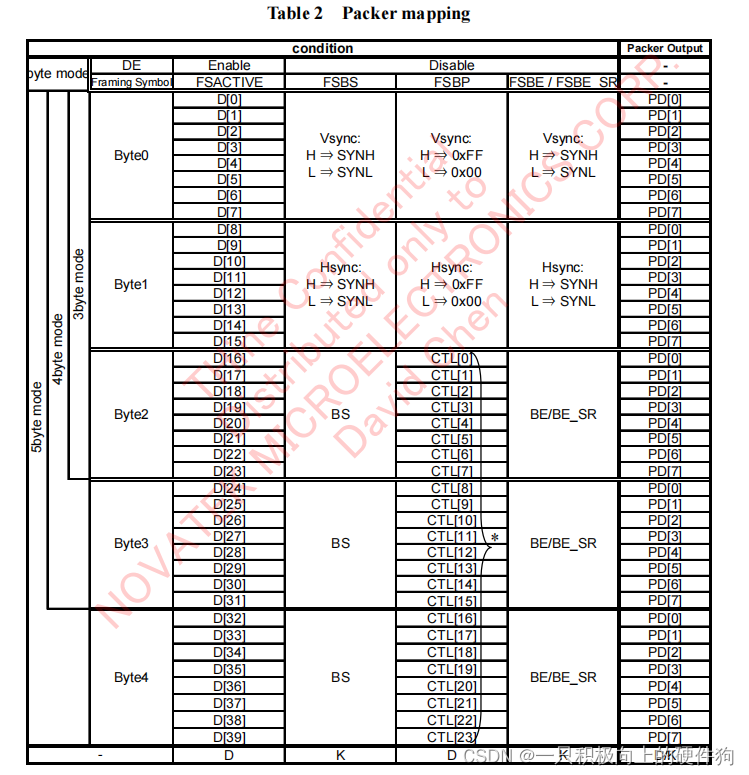

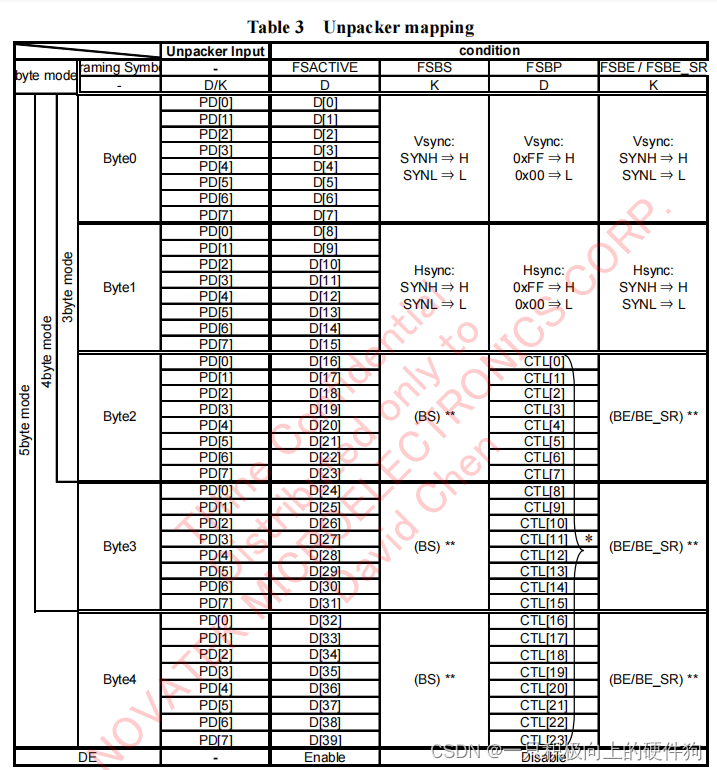

一个packet由8bit数据组成;Packet的数据包括:有效数据(data),控制信号(CTL),时序信号(DE,H-sync,V-sync),packet的data mapping由帧byte决定;打包后的数据顺序为高位在后,低位在前。D/K码是用于8bit/10bit扰码器的抽头选择。

(1)data mapping

名词介绍:

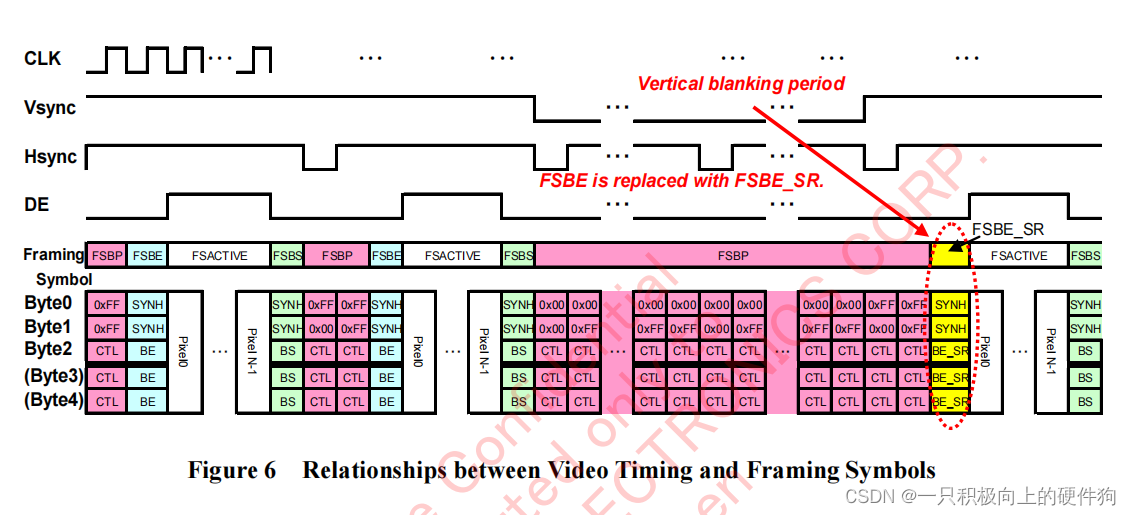

FS:framing symbols 帧符

FSACTIVE:Pixel Data在DE为高电平时被打包,在此期间的所有data均为D code

FSBS:Blanking Start 在pixel data的最后一个后插入,V sync和H sync被打包在byte0和byte1中;在此期间的所用data,均为K code

FSBP:Blanking Payload 插入在BS和BE之间;V sync和H sync数据被打包在Byte0和Byte1中,将CTL数据打包在Byte2-4中。在此期间的数据,均为K code

FSBE:Blanking End 插入在第一个像素之前。在此期间的数据均为K code

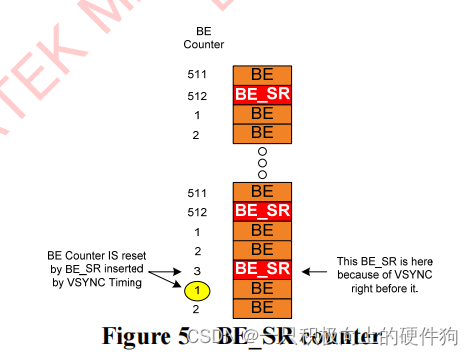

FSBE_SR:在Vsync后的第一个FSBE和每512个FSBE被FSBE_SR取代,用于重置LFSR(liner feedback shift register)。每次发送FSBE_SR时,FSBE将被重置。

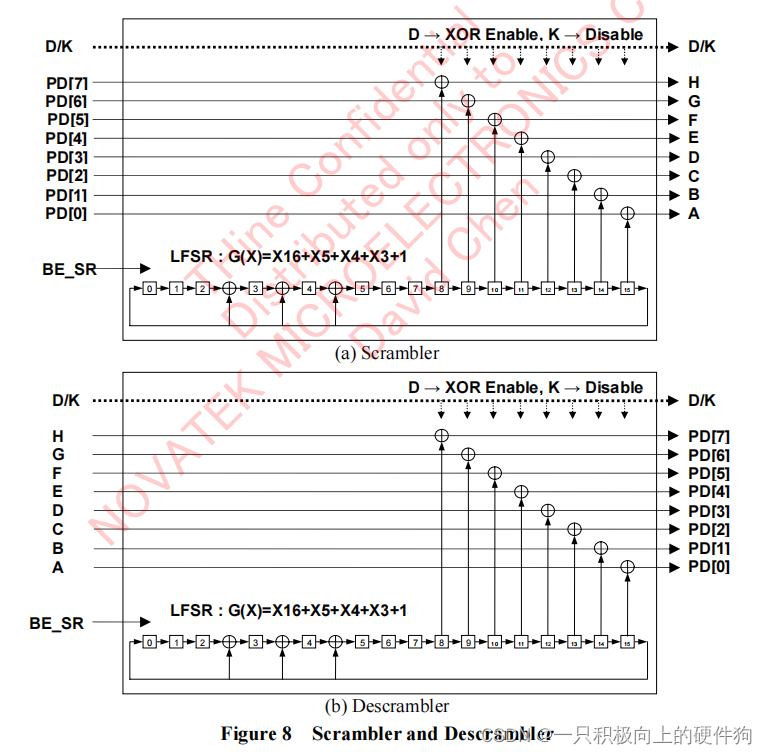

2、Scrambler and Unscrambler

在8bit/10bit encoder之前,先进性扰码处理;来减轻EMI问题;每条line,独立使用16位LFSR进行扰码处理。

16位LFSR的G(X)=X16+X5+X4+X3+1

BS,BE,SYNL,SYNH,BE_SR不能被扰码,BP及FSACTIVE可以被扰码;在CDR training阶段的Scrambler必须disable。3

3、encode and decode

编码器和解码器与ANSI标准8b/10b兼容。在正常的模式操作中,每个10位的字符代表8位的像素数据(图11)。编码字符在V-by-One®HS流中提供直流平衡和足够的0-1和1-0转换,使接收机能够使用CDR技术恢复链路时钟。

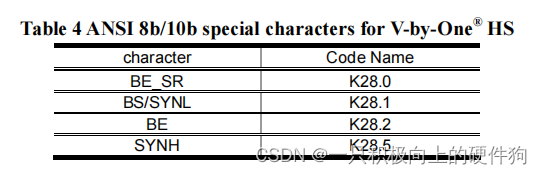

FSBS、FSBE、FSBE_SR帧符号由K码组成,FSBP帧符号由D码组成。FSBS框架符号由BS、SYNH或SYNL字符组成,而FSBE符号除包含SYNH或SYNL字符外,还包含BE或BE_SR字符。下表中描述了SYNH、SYNL、BS、BE和BE_SR等特殊字符。BS和SYNL被分配了相同的代码。BS、SYNH和SYNL代码也称为COMMA,它们用于检测字节边界。

4、Serializer and Deserializer

评论记录:

回复评论: