FPGA现场可编程逻辑阵列,使用它不仅要有强大的硬件语言编辑能力,更要熟练的使用Verilog、HDL、VHDL语言,还要对硬件电路电子电路有着详细的了解,要对FPGA最小运行系统电路I/O端口有着了解应用。

本文目的和配套资源:

详细讲解FPGA最小运行系统每个引脚的应用和定义,并按照重要等级排序(本文是按照赛灵思XC7Z020CLG400-2 FPGA介绍展开的)

配套资源说明:解压后打开文件看到三个文件他们的作用分别是:

No.01:该文章主要围绕着这个原理图进行讲解。

No.02:赛灵思官网(AMD)下载的部分配套资料。

No.03:XC7Z020其他原理图,仅供参考。

UG585技术手册是关于芯片引脚和技术的说明,内含英文原文,和Deelp翻译(有部分翻译有误,和大量串页不影响阅读)

供电引脚选择说明:

详细引脚功能说明参考No.02(ds187-XC7Z010-XC7Z020-Data-Sheet (1))资料

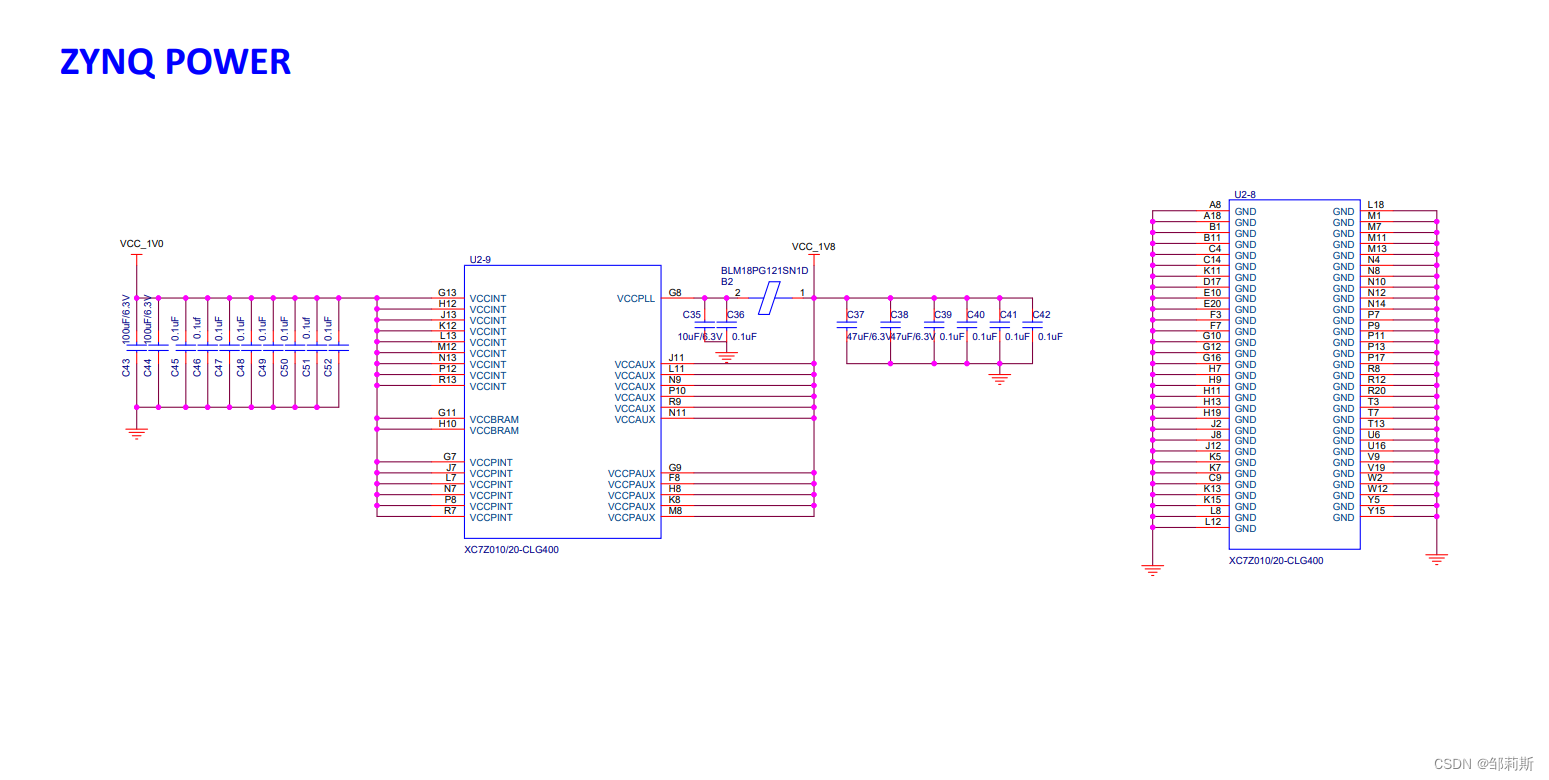

主要供电部分参照原理图No.01第六页。

主供电引脚说明:

主要供电部分,不能缺失缺失会引起FPGA无法正常工作。

GND部分:

GND引脚,和普通电子电路GND引脚作用相同,GND就是公共端的意思,也可以说是地,是一个电源的负极,和VCC相对应,注意是单电源供电,GND连接着电源的负极,在上图有很多个引脚连接着GND,不要落下任何一个GND引脚和供电的负极相连,否则会引起意想不到的后果。

PS端:

VCCPINT:

VCCPINT为FPGA内核逻辑供电引脚,内部基本逻辑供电FPGA逻辑网络供电,必须按照数据手册电压连接。

VCCPAUX:

VCCPAUX为PS系统辅助供电引脚,辅助电源电压,必须按照数据手册电压连接。

VCCPLL:

VCCPLL电压PS端辅助部分,在硬件上有特殊要求(使用时要在该引脚串联磁环电感并保证靠近引脚,减少干扰),应当注意。

VCCO_DDR:

VCCO_DDR引脚作用是连接FPGA外部RAM存储器供电电源部分,必须保证该引脚的电压要和RAM存储器主供电电压一致。

VCCO_MIO:

PS端I/O端口电压,电平标准,表示该引脚的输入电压就是PS端口(I/O接口)电压,在这里我觉得他应该叫PS_VCCO_MIO会更好。

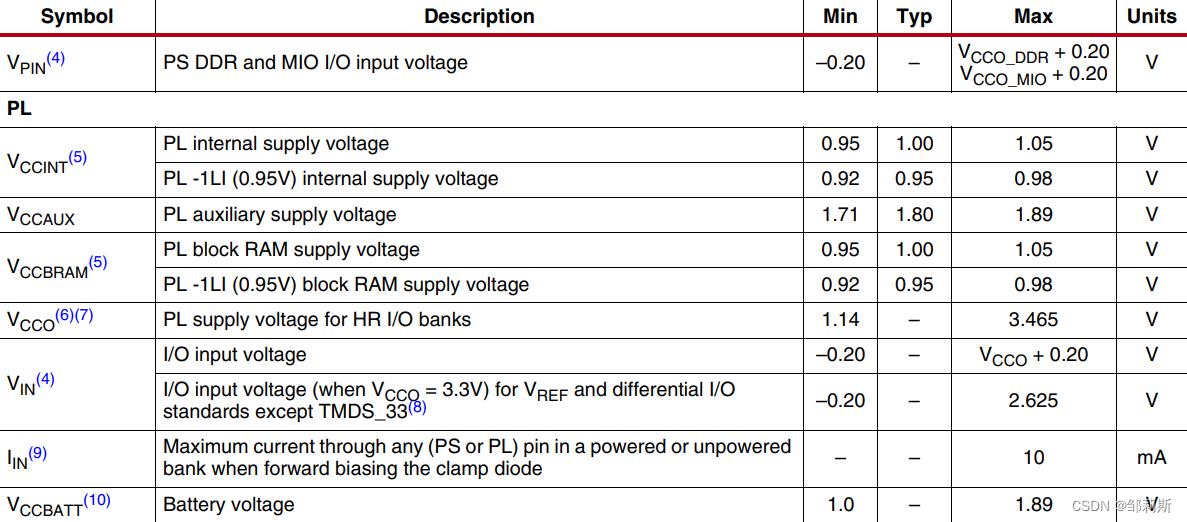

VPIN:

VPIN是PS端DDR和PS端MIO输入电压,该引脚使用的较少,一般当做PS端的辅助供电引脚,或在芯片内部提供提供偏置,它的最大电压由VCCO_DDR和VCCO_MIO电压决定其关系是:VCCO_DDR比较VCCO_MIO最大的加上0.2V就是VPIN引脚的最大电压。

PL端:

VCCINT:

VCCINT是FPGA芯片的内核电压,是用来给FPGA内部的逻辑门和触发器上的电压。即芯片的晶体管开关是由核心电压提供。当内部逻辑工作时钟速率越高,使用逻辑资源越多,则核心电压供电电流会更大,可高达几安,此时芯片必然会发烫,需要散热装置辅助散热。

VCCAUX:

FPGA并非一个单纯的数字逻辑芯片,内部也带有一些模拟组件,比如Xilinx的DCM数字时钟管理组件、高档点的FPGA还有高速串并转换器serdes、温度监控器件等这些模拟器件,这些模拟器件对电源噪声要求很高,所以需要一个独立稳定的电源进行供电。Vccaux就是为这些模拟器件提供电压,另外Vccaux还可以给部分IO供电,像JTAG等。

VCCBRAM:

VCCBRAM为FPGA Block RAM的供电引脚,FPGA内嵌的块RAM存储器的供电电压,因为FPGA片上RAM存储器由内部PL端逻辑负责控制,对芯片内部逻辑数据暂时存储。

VCCO:

VCCO端口电压,电平标准,表示该引脚的输入电压就是PL端口(I/O接口)电压,在这里我觉得他应该叫PL_VCCO_MIO会更好。

VIN:

VIN引脚电压输入引脚应该作用于VCCO电压钳位,VREF和差分I/O的I/O输入电压(当VCCO = 3.3V时)

IIN :

IIN正向偏置钳位二极管,作用在(PS或PL)端电流输入,保证最大电流输出的钳位,注意每个PS或PL组总电流不应超过200MA,对应原理图4页,连接4.7K上拉电阻限制电流(应该是原理图和官方手册有轻微出入)。

VCCBATT:

该引脚是FPGA内部易失性存储器的电池备用电源,用于存储AES解密器的密钥,如果不需要使用AES易失性密钥存储区域中的解密器密钥,那么将该引脚接地就行,根据部分参数手册说明该引脚可以连接至VCCAUX电源引脚,该引脚不是I/O,不受VCCO_0的影响。了解该引脚功能即可,此引脚在BANK0部分在原理图第4页。

不同端口组选择电压说明:

为了保证FPGA在使用的时候可以连接不同电平的外接设备,于是采用端口分组的方式来连接不同电平接口,这样就可以同时连接着EMMC存储器一边连接着3.3V输出电平的I/O,为了保证正常的使用,搞清楚接口组的使用方法就会变得很重要。

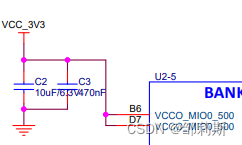

VCCO_MIO0_500:

VCCO_MIO0_500供电引脚,参照原理图No.01第二页,对应_500的引脚的供电该引脚的供电是针对_500引脚独立的供电,不对其他引脚组产生影响,该引脚的供电电压由外部器件I/O接口最高电平电压决定,该引脚组涉及到芯片逻辑内核部分,注意该引脚的电压不要超过参数手册的最大电压。

VCCO_MIO1_501:

VCCO_MIO1_501供电引脚,参照原理图No.01第二页,对应_501的引脚的供电,该引脚的供电是针对_501引脚独立的供电,不对其他引脚组产生影响,该引脚的供电电压由外部器件I/O接口最高电平电压决定,该引脚组涉及到芯片逻辑内核部分,注意该引脚的电压不要超过参数手册的最大电压。

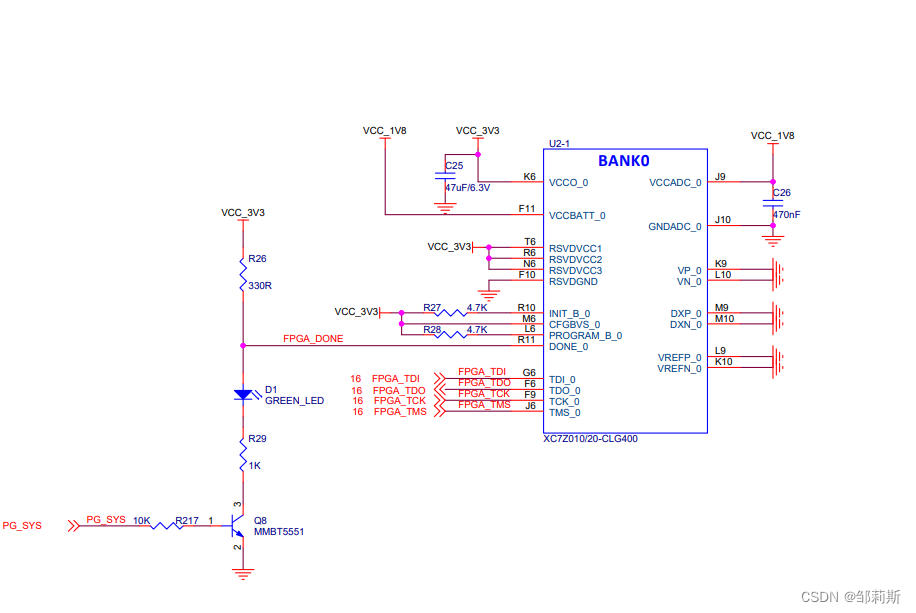

VCCO_0:

VCCO_0供电引脚,参照原理图No.01第四页,对应_0的引脚的供电该引脚的供电,是针对_0引脚独立的供电,不对其他引脚组产生影响,该引脚的供电电压由外部器件I/O接口最高电平电压决定,注意该引脚的电压不要超过参数手册的最大电压, 该引脚组在FPGA中特殊,属于内核系统控制引脚,该引脚组不能当普通I/O引脚使用,在下文会对该部分进行介绍。

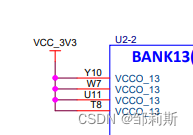

VCCO_13:

VCCO_13供电引脚,参照原理图No.01第四页(只有局部引脚在原理图中),对应_13的引脚的供电,该引脚的供电是针对_13引脚独立的供电,不对其他引脚组产生影响,该引脚的供电电压由外部器件I/O接口最高电平电压决定,注意该引脚的电压不要超过参数手册的最大电压,连接普通I/O接口输入输出功能。

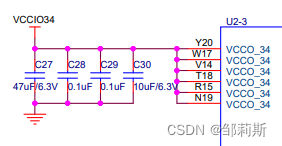

VCCO_34:

VCCO_34供电引脚,参照原理图No.01第五页(只有局部引脚在原理图中),对应_34的引脚的供电,该引脚的供电是针对_34引脚独立的供电,不对其他引脚组产生影响,该引脚的供电电压由外部器件I/O接口最高电平电压决定,注意该引脚的电压不要超过参数手册的最大电压,连接普通I/O接口输入输出功能。

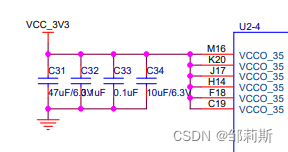

VCCO_35:

VCCO_35供电引脚,参照原理图No.01第五页(只有局部引脚在原理图中),对应_34的引脚的供电,该引脚的供电是针对_34引脚独立的供电,不对其他引脚组产生影响,该引脚的供电电压由外部器件I/O接口最高电平电压决定,注意该引脚的电压不要超过参数手册的最大电压,连接普通I/O接口输入输出功能。

系统运行控制部分:

为了保证FPGA系统能够合理的在电路板上运行,除了供电部分为FPGA提供压还需要局部外部电路对内部运行系统进行控制。

上电复位:

FPGA上电复位引脚在PS端,参照No.01原理图2页,对应硬件BGA编号C7,端口编号PS_POR_B_500,低电平复位有效,默认时保持高电平(上拉状态),不同的数量的BGA引脚对应的编号点数有所不同。

以下是对应等效原理图(低电平复位):

为了保证电路能稳定工作, 建议在复位引脚上加上监控和复位芯片,(复位有效电平:低电平),保证功能掉电复位和上电复位。

系统主时钟设定:

FPGA 主时钟引脚在PS端,参照No.01原理图2页,对应硬件BGA编号E7,端口编号PS_CLK_500 ,不同的数量的BGA引脚对应的编号点数有所不同。

以下是PS端晶振系统参考时钟输入要求,

PS_CLK引脚是必须要设定有源晶振的,如果不设定导致FPGA芯片无法工作, 晶振的选择只能是有源晶振,因为FPGA芯片只有晶振输入引脚,频率范围要按照数据手册的要求设定。

系统控制部分引脚组VCCO_0:

VCCO_0组引脚几乎都是对系统进行控制的,不能当通用I/O来使用。

RSVDVCC1、RSVDVCC2、RSVDVCC3:

RSVDVCC1 保留引脚,必须保证电压要和VCCO_0一致。

RSVDVCC2 保留引脚,必须保证电压要和VCCO_0一致。

RSVDVCC3 保留引脚,必须保证电压要和VCCO_0一致。

也有的把这些引脚叫RSVDVCC[3:1],其实他们都是一个意思。

RSVDGND:

RSVDGND 保留引脚,和上三个引脚相对应, 必须连在GND保证电路的稳定。

INIT_B_0:

上电为低电平模式,完成初始化后转变为高阻态,参照原理图上拉电阻应到和VCCO_0相同电压的电源,高电平后执行后续操作可以在芯片上电时强行拉低,拉低该引脚延迟FPGA器件的配置过程,不建议这样操作,建议参照原理图内容上拉4.7K电阻到VCCO电压。

CFGBVS_0:

CFGBVS_0该引脚决定了BANK部分的电平标准,用处较少,有些器件没有这个引脚,一般把它作为下拉(参照原理图),不会影响器件正常运行。

PROGRAM_B_0:

重新配置引脚,低电平触发该功能,把程序数据清零并重新下载,下降沿复位,上升沿启动重新配置,官方数据手册建议通过≥4.7K电阻上拉到VCCO_0,通过开关连接到GND,用来手动清除内部程序的数据,当该引脚为一直为低时不会一直复位。

DONE_0:

DONE_0 双向专用引脚,高有效,表示FPGA配置完成,也可以表示下载完成指示,通常在该引脚连接1个LED灯,表示数据已经下载完成,内有10K上拉电阻,可以悬空,可以330R上拉电阻。

TCK_0 、TDI_0 、TDO_0 、TMS_0 :

TCK_0、JTAJG数据输入引脚,建议加防静电措施(TVS管)下载程序专用接口,JTAG时钟。

TDI_0、 JTAJG数据输入引脚,建议加防静电措施(TVS管)下载程序专用,JTAG数据输入。

TDO_0、JTAJG数据输出引脚,建议加防静电措施(TVS管)下载程序专用,JTAG数据输出。

TMS_0 、JTAJG数据输入引脚,建议加防静电措施(TVS管)下载程序专用,JTAG模式选择 。

VCCADC_0、GNDADC_0:

VCCADC_0:XADC 中ADC 和其他模拟电路的模拟电源引脚,电压和VCCAUX保持一致,建议单独供电或通过滤波电路(电感等)连到VCCAUX上,以保证尽量减少信号的干扰,从而影响采集的精度,不使用时也需要接VCCAUX。

GNDADC_0:XADC的模拟接地引脚,应该通过磁珠连接到系统GND。在一个混合信号系统中,如果可能的话,此引脚应该连到在一个模拟的接地平面上,在这种情况下就可以不需要铁氧体磁珠。即使XADC 不用,也应始终将此引脚连接到GND。

VP_0、VN_0:

VP_0/VN_0:XADC专用差分输入引脚(专用是对比其他XADC模拟输入来说,该引脚不能用作普通IO,其他的都可以),不使用时接GND;

专用模拟输入VP/VN 采用差分采样方案,以减少共模噪声信号的影响。PCB 的公共地阻抗将数字电路的开关电流噪音耦合到模拟系统,其幅度可达100 毫伏或更高。这对于ADC 来说相当于数百个LSB,因此会导致很大的测量误差。差分采样方案在两个输入端(VP/VN)对含共模噪声的信号进行采样。ADC 的前置放大器的高共模抑制比有效地抑制了共模噪声信号,送到ADC 输入口的只剩下VP 和VN 之间的差模信号。所以用户如果要获得高共模抑制比,应采用专用模拟输入通道VP/VN。

DXP_0、DXN_0:

DXP_0、DXN_0 为内部热敏二极管温度传感器引脚,在BANK0热二极管被允许接入使用DXP和DXN引脚,结合外部温度监控电路可实现对FPGA芯片内部温度的监控,不用时接系统GND。在设计该部分电路时,可以使用MAX6642替代热敏二极管。大多数热敏二极管温度传感器,包括MAX1617和MAX6654,与二极管都有两个连接点:DXP和DXN。DXP连接至热敏二极管的阳极,源出二极管偏置电流。DXN吸入偏置电流,并将阴极偏置在0.7V左右。

VREFP_0、VREFN_0:

VREFP_0、VREFN_0电压基准,电压基准GND,此引脚可连接到外部1.25V 精确参考IC(±0.2%或12 位的±9 LSB),以获得ADC 的最佳性能。应将其视为模拟信号,与VREFN 信号一起提供1.25V 差分电压。如果将VREFP_0引脚连接到GNDADC,芯片内参考源(12 位时为±1%或±41 LSB)被激活。如果没有提供外部引用,这个引脚应该应始终连接到GNDADC(GND)。

其他PUDC_B(XC7Z020没有):

PUDC_B 多功能,输入,在配置的时候上拉,当上电后和在配置的过程中,低有效的PUDC_B引脚输入在选择的输入输出引脚上使能内部上拉电阻。这个引脚低的时候,在每个SelectIO引脚内部上拉电阻使能;当高的时候,内部上拉电阻不使能。这个引脚必须直接接地。不允许在配置前和配置的时候悬空

系统控制部分引脚组VCCO_0 部分内容参考作者:硬件光阴 https://www.bilibili.com/read/cv26635057/ 出处:bilibili

程序资源存储选择部分 :

按照上面的需要进行设定光有了程序运行的硬件环境还不够,还要有存储程序部分的存储器,这就包括了让FPGA从哪里进行启动,读取哪里的数据。

按照芯片功能BANK500和BANK501 端的引脚和内部内核控制器相连,本身这两组的GPIO不同于普通I/O组(BANK13、BANK34、BANK35),在官方设定中BANK0、BANK500、BANK501、BANK502(内存接口引脚组)、都是有特殊的定义的,尽量不要当做普通的I/O接口来使用,注意BANK502是一点都不能当做通用I/O使用,BANK500、BANK502可以当做通用I/O不过更适合复杂,速度快,稳定的输出设备,

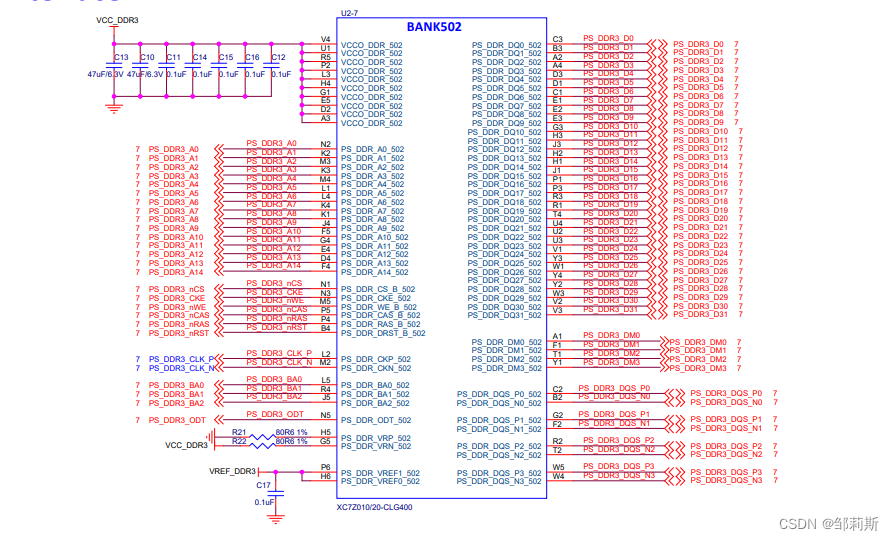

内存RAM引脚 :

内存引脚部分由BANK502引脚组占有 可以参照原理图的第三页,内存部分可以参照第七页,供电部分由内存供电单独供应,注意BANK502组的引脚组不能当普通I/O接口来使用,

DDR3内存部分,可以参照原理图连接,。

BOOT模式选择:

选择好BOOT设定启动时由BOOT来决定数据从什么地方中开始运行。

PS_MIO2_500:BOOT模式或SPI模式可以连接BOOT选择机制或者连接外置FLASH对应QSPI原理图引脚QSPI _ DQ0端口,很少用在BOOT选择机制引脚,一般把该引脚下拉,更详细内容可以参照附带资料的参数手册(有翻译)。

PS_MIO3_500:BOOT模式或SPI模式可以连接BOOT选择机制或者连接外置FLASH对应QSPI原理图引脚QSPI _ DQ1端口,很少用在BOOT选择机制引脚,一般把该引脚下拉,更详细内容可以参照附带资料的参数手册(有翻译)。

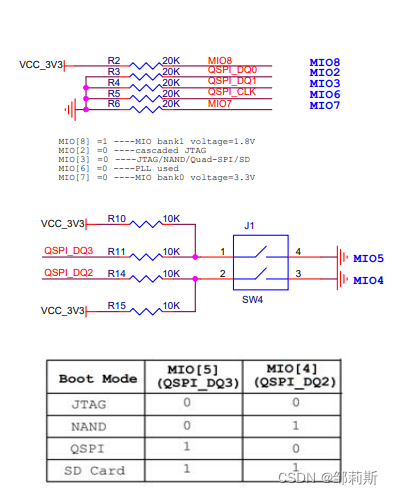

PS_MIO4_500、PS_MIO5_500:

下图的 PS_MIO4_500对应着QSPI_DQ2,PS_MIO5_500对应着QSPI_DQ2,

把这两个引脚一起说是因为这两个主要控制着BOOT模式, 从上图中可以看出MIO_5和MIO_4全下拉FPGA进入JTAG模式、MIO_5下拉MIO_4上拉FPGA进入NAND模式、MIO_5下拉MIO_4上拉FPGA进入QSPI模式、MIO_5和MIO_4全上拉FPGA进入SD CARD模式、注意这两个引脚还和QSPI模式的端口相连,下拉的电阻不要太小或太大,MIO_5对应QSPI的DQ3,MIO_4对应QSPI的DQ2,在使用时应该注意。

PS_MIO6_500:BOOT模式或SPI模式可以连接BOOT选择机制或者连接外置FLASH对应QSPI原理图引脚QSPI _ CLK端口,很少用在BOOT选择机制引脚,一般把该引脚下拉,更详细内容可以参照附带资料的参数手册(有翻译)。

PS_MIO7_500:BOOT模式或SPI模式可以连接BOOT选择机制,很少用在BOOT选择机制引脚,一般把该引脚下拉,更详细内容可以参照附带资料的参数手册(有翻译)。

PS_MIO8_500:BOOT模式或SPI模式可以连接BOOT选择机制,很少用在BOOT选择机制引脚,一般把该引脚上拉,更详细内容可以参照附带资料的参数手册(有翻译)。

JTAG模式:

现场调试模式,传入数据断电后丢失,适合现场调试使用,MIO_5和MIO_4全下拉FPGA进入JTAG模式,对应的JTAG模式下载引脚在BANK0中。可以用于所有模式的数据的下载,JTAG只是设定内部数据只存在RAM中,不和任何存储器相关,其中和JTAG下载的引脚无关,只是用来传输的,模式是模式,下载引脚是下载引脚,两个不关联,独立的。

下载引脚通用,并不是JTAG模式专用的引脚。

NAND模式:

NAND模式,MIO_5下拉MIO_4上拉FPGA进入NAND模式,使用片外存储器,适合程序较大的数据,但是原理图未给出,说明使用较少,不是很常用,或许和哪些下拉或上拉的BOOT引脚有关。

占用BANK501组的引脚,详细内容参见附带资料的部分,参见No.02官方数据手册,或在Xilinx官网下载资料。

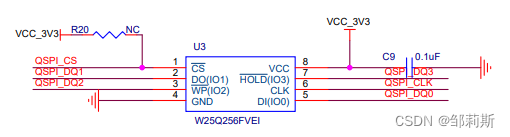

QSPI模式:

把数据存储在片外的FLASH中,MIO_5下拉MIO_4上拉FPGA进入QSPI模式,断电后保存数据需要做QSPI固化才能保存程序数据,再次开启后是QSPI模式时按照FLASH中数据运行程序。

PS_MIO1_500:对应QSPI芯片引脚QSPI _ CS。

PS_MIO2_500:对应QSPI芯片引脚QSPI _ DQ0,注意该引脚和BOOT模式引脚相连。

PS_MIO3_500:对应QSPI芯片引脚QSPI _ DQ1,注意该引脚和BOOT模式引脚相连。

PS_MIO4_500:对应QSPI芯片引脚QSPI _ DQ2,注意该引脚和BOOT模式选择功能引脚相连,不影响使用。

PS_MIO5_500:对应QSPI芯片引脚QSPI _ DQ3,注意该引脚和BOOT模式选择功能引脚相连,不影响使用。

PS_MIO6_500:对应QSPI芯片引脚QSPI _ CLK,为了保证CLK时钟的准确要和原理图那样串联33R的电阻,注意该引脚和BOOT模式引脚相连。

QSPI芯片的选择注意它的工作电压和BANK500组的电压,保证QSPI器件的工作电压范围在BANK500组的I/O电压范围就行。

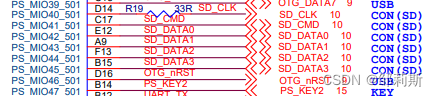

SD CARD模式:

SD卡模式,数据保存到外置SD卡中,MIO_5和MIO_4全上拉FPGA进入SD CARD模式,设定好BOOT下次启动时从SD卡内部的数据启动,这里原理图中采用的是可插拔TF卡,用于做FPGA片上Linux系统使用。

参见原理图第十页, 这里采用了一个SD卡信号的转换器,原理图是这样的,但是在官方设定时不一定和这一样,

但在原理图中使用是:

PS_MIO41_501:对应着SD卡的SD_CLK引脚,为了保证CLK时钟的准确要和原理图那样串联33R的电阻。

PS_MIO41_501:对应着SD卡的SD_CMD引脚。

PS_MIO41_501:对应着SD卡的SD_DATA0引脚。

PS_MIO41_501:对应着SD卡的SD_DATA1引脚。

PS_MIO41_501:对应着SD卡的SD_DATA2引脚。

PS_MIO41_501:对应着SD卡的SD_DATA3引脚。

注意:从FPGA引出来的这些引脚可以看出并不是标准的SD卡协议,而是通过转换芯片转换的,这些引脚的排列更像是一个外接存储器。

结尾:

到这里该文章的内容就结束了,我讲解的是针对XC7Z020CLG400-2芯片的,不过在大多数的FPGA芯片中都通用。

全文共计8267字看到这了,你有没有对自己的问题有所解答呢?有问题欢迎随时指出,我会及时更正的,谢谢啦。

评论记录:

回复评论: