名称:模式切换控制电路设计Verilog代码vivado ego1开发板(文末获取)

软件:vivado

语言:Verilog

代码功能:

利用 Verilog3HDL设计一个逻辑控制电路、用于对某备进行模式切换控制、设备模式共三种,控制方式为

直通模式:高电平为直通有效、接地为直通无效

跳频模式:接地为跳频模式有效,高电平跳频无数

调谐模式:接地为调谐模式有效、高电平调谐无效

设备的同一时刻只有且必颊有一个模式有效,其他两个无效,为防止同时个模有效、模式切换之间应有较小的延时,利用按键作为三种模式切换输入(按键最有消除扦动的措施

设计要求:

(1)编写源程序

(2)给出仿真电路团和仿真波形图

(3)开发板实物验证

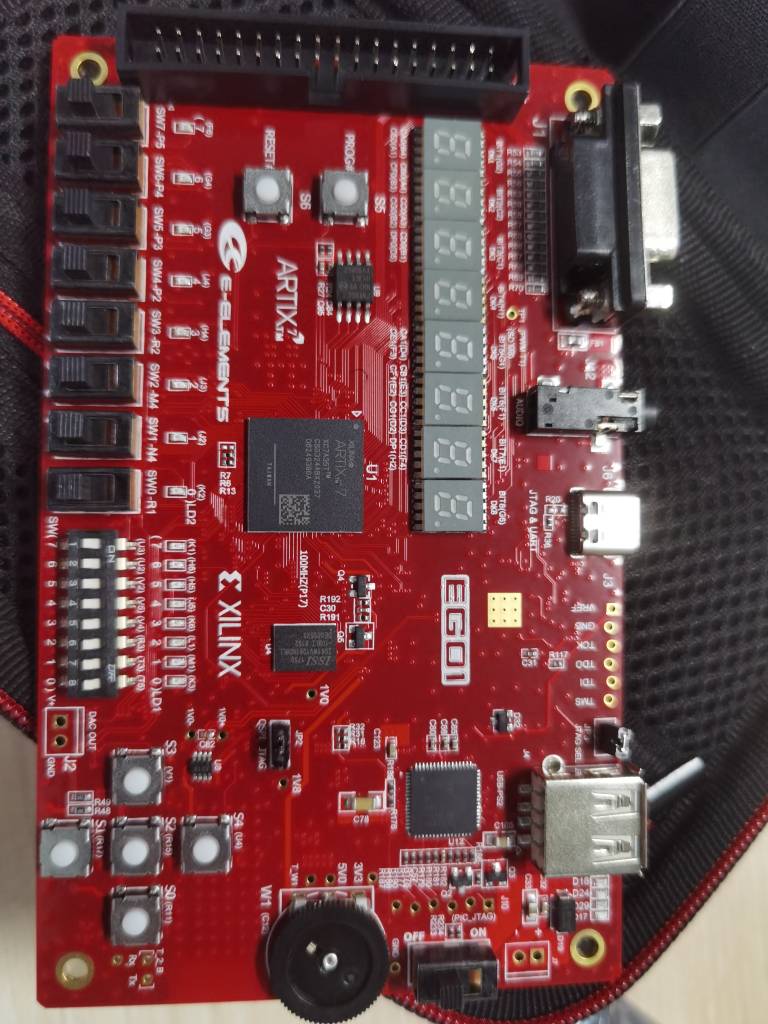

本代码已ego1开发板验证,ego1开发板如下,其他开发板可以修改管脚适配:

1. 工程文件

2. 程序文件

3. 程序编译

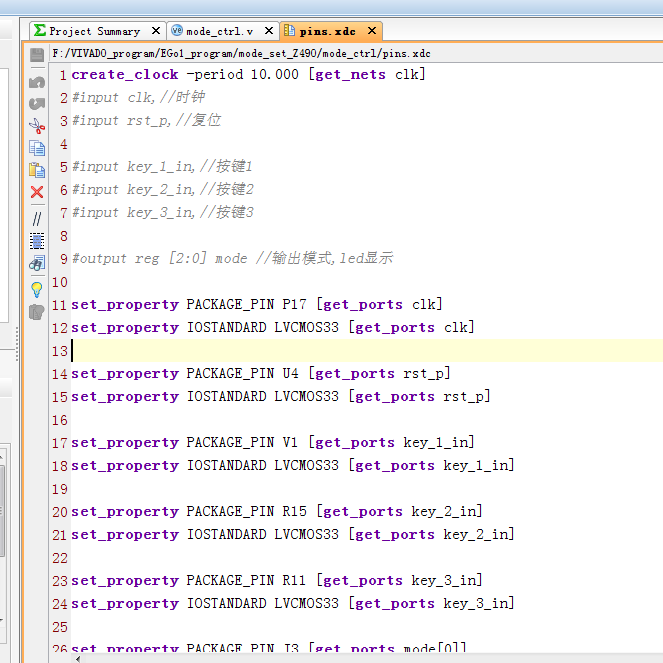

4. 管脚分配

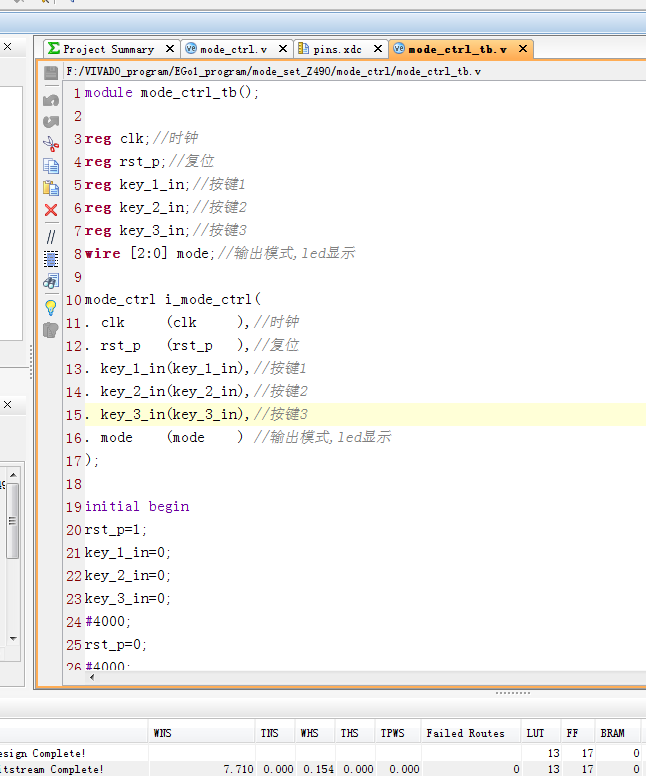

5. Testbench

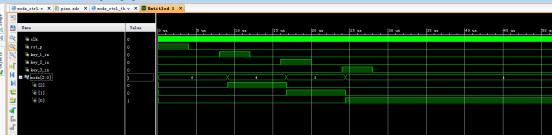

6. 仿真图

部分代码展示:

module mode_ctrl( input clk,//时钟 input rst_p,//复位 input key_1_in,//按键1 input key_2_in,//按键2 input key_3_in,//按键3 output reg [2:0] mode //输出模式,led显示 ); wire key_1;//消抖后按键1 wire key_2;//消抖后按键2 wire key_3;//消抖后按键3 //按键消抖 reg key_1_buf0; reg key_2_buf0; reg key_3_buf0; reg key_1_buf1; reg key_2_buf1; reg key_3_buf1; //延迟计数器 reg [7:0] cnt_base=8'd0; always@(posedge clk or negedge rst_p) if(rst_p) cnt_base <= 8'd0; else cnt_base <= cnt_base + 8'd1; //输出 always@(posedge clk) if(cnt_base==8'hff)begin//延迟计数后采样 key_1_buf0 <= key_1_in; key_2_buf0 <= key_2_in; key_3_buf0 <= key_3_in; end //触发器打拍 always@(posedge clk) begin key_1_buf1 <= key_1_buf0;//触发器打拍 key_2_buf1 <= key_2_buf0;//触发器打拍 key_3_buf1 <= key_3_buf0;//触发器打拍 end assign key_1=key_1_buf0 & !key_1_buf1;//消抖后按键1 assign key_2=key_2_buf0 & !key_2_buf1;//消抖后按键2 assign key_3=key_3_buf0 & !key_3_buf1;//消抖后按键3 always@(posedge clk or negedge rst_p) begin if(rst_p) mode<=3'b000;//复位 else if(key_1)//按键1 mode<=3'b100;//指示模式1 else if(key_2)//按键2 mode<=3'b010;//指示模式2 else if(key_3)//按键3 mode<=3'b001;//指示模式3 end endmodule

源代码

扫描文章末尾的公众号二维码

FPGA代码设计学习资料

微信公众号

微信公众号

FPGA代码设计资料

微信公众号

微信公众号

评论记录:

回复评论: