前言:

对于一个完整的项目开发来说,跑仿真是必不可少的,用户可以通过仿真去检查代码中的逻辑性错误,以及观察功能是否能够实现。在这里我将去介绍vivado平台所自带的仿真Simulation

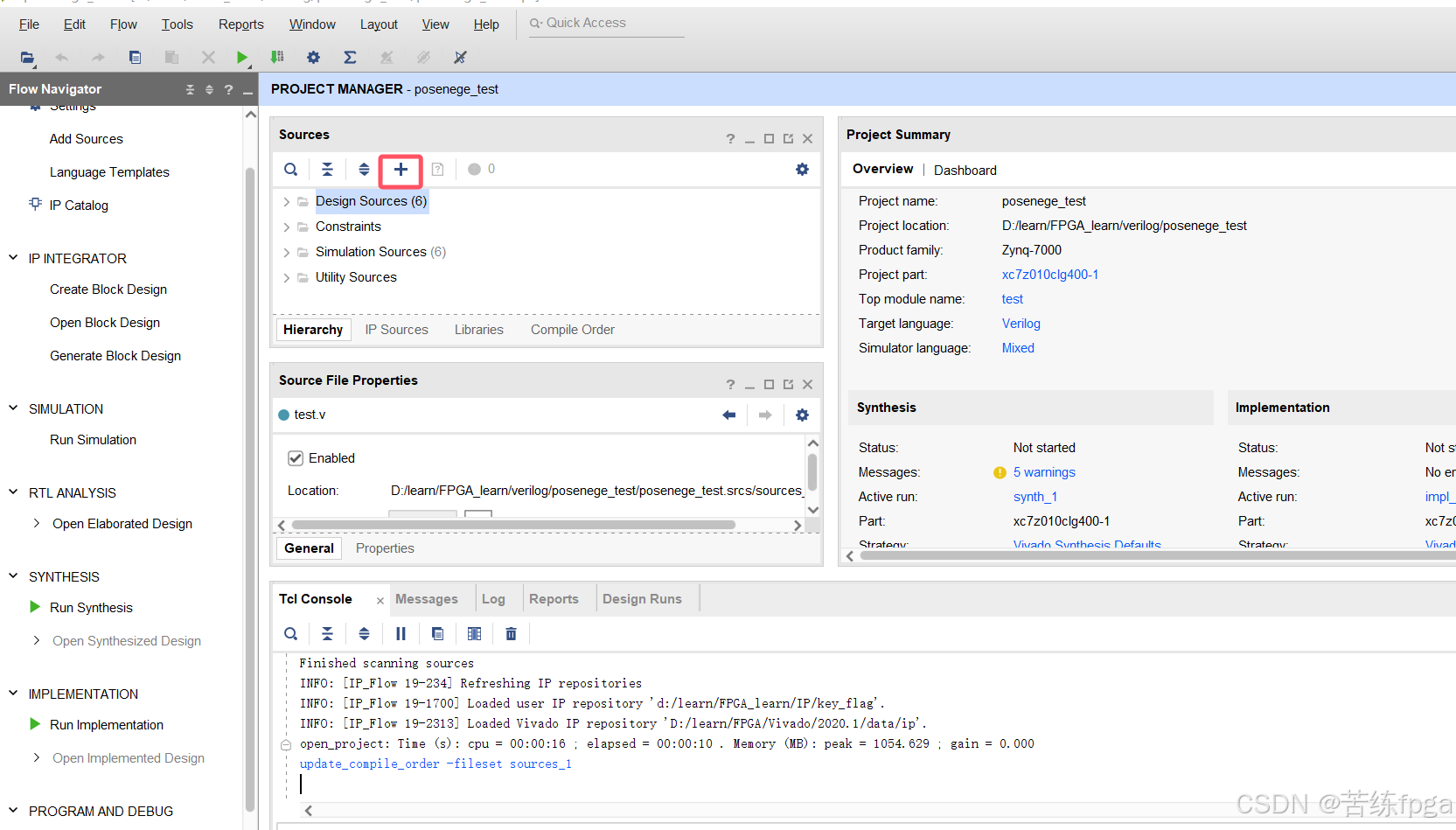

创建仿真文件:

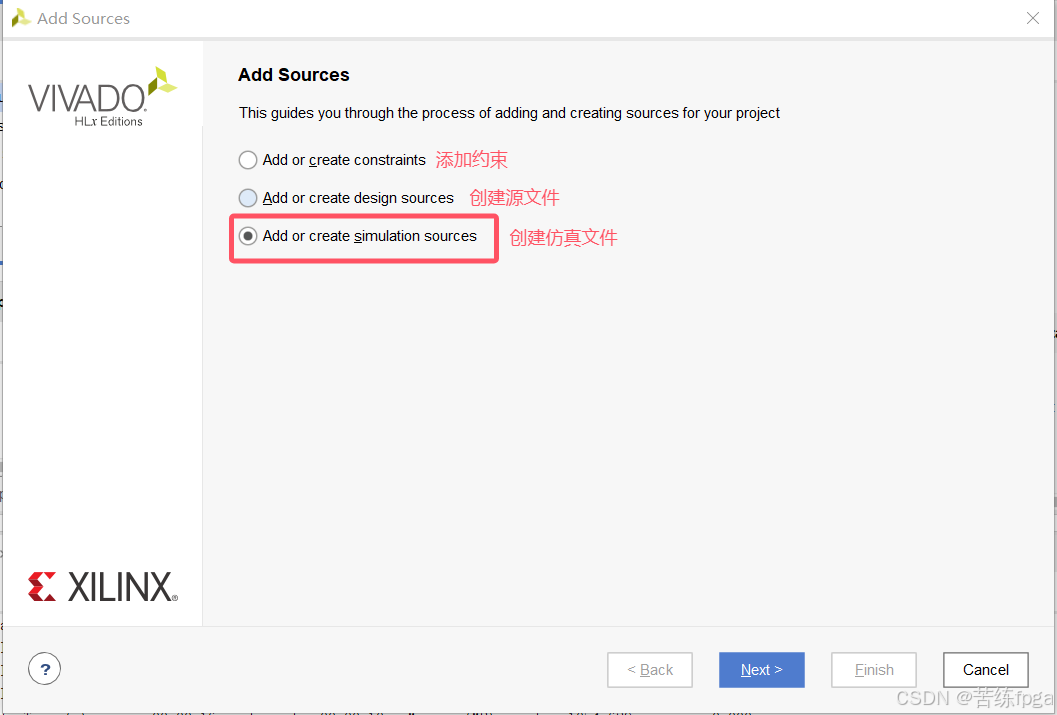

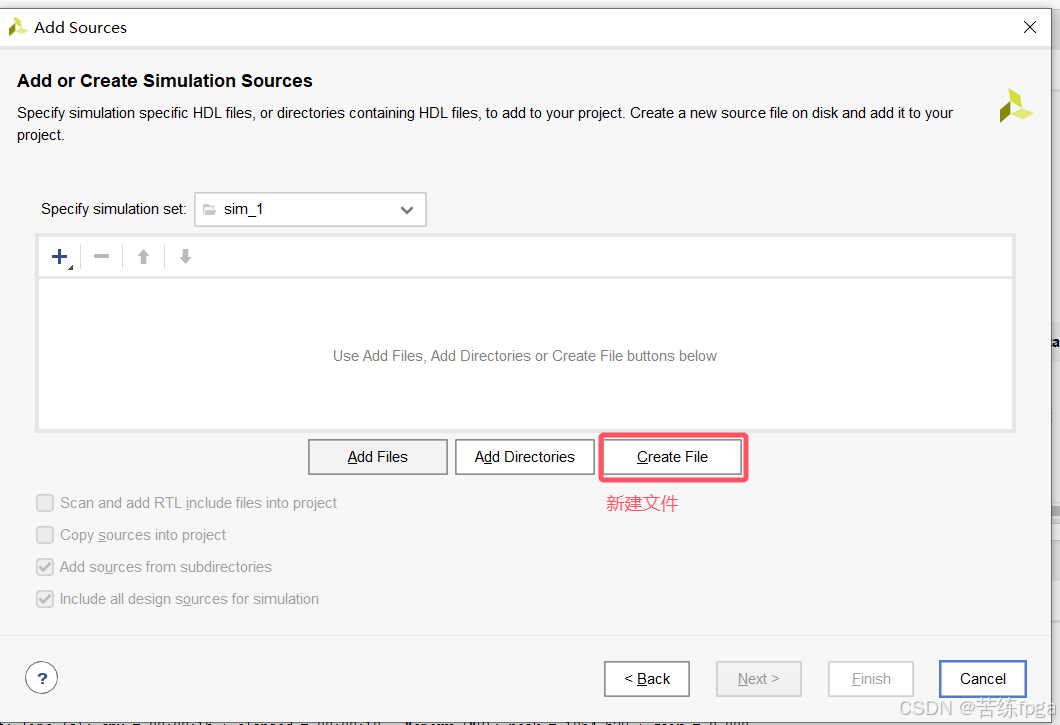

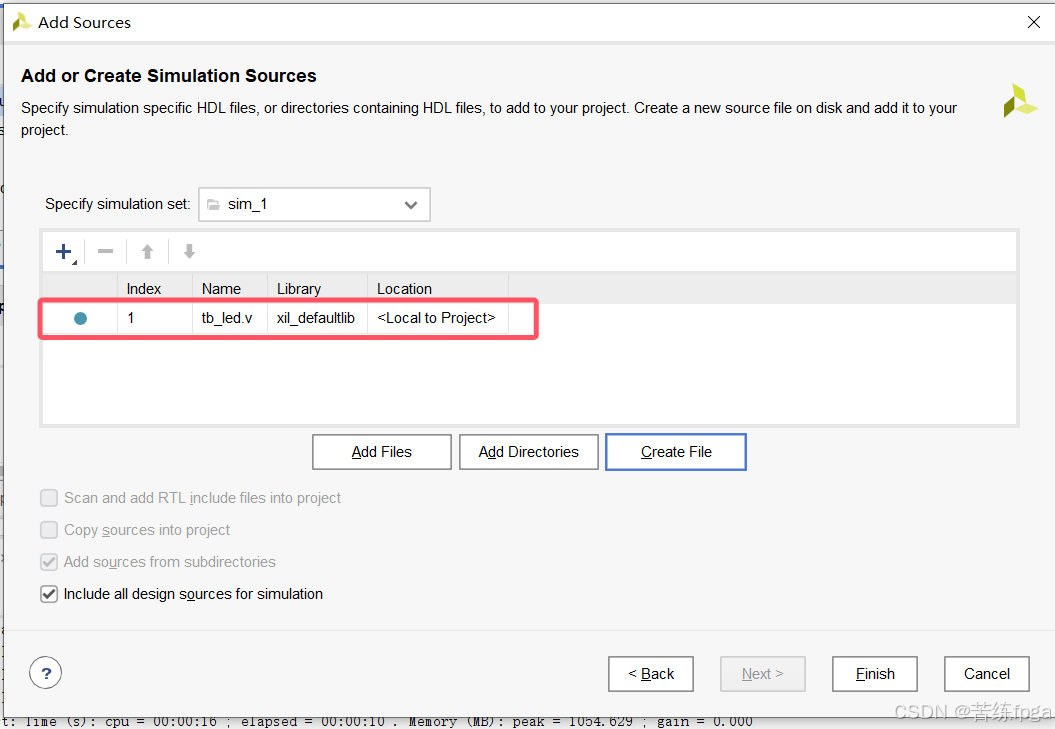

选择第三个新建仿真文件

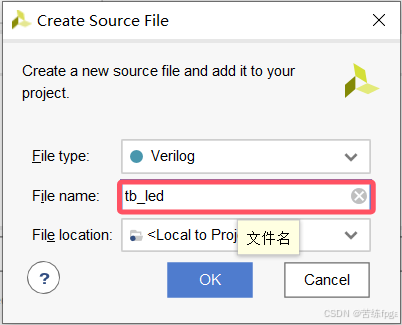

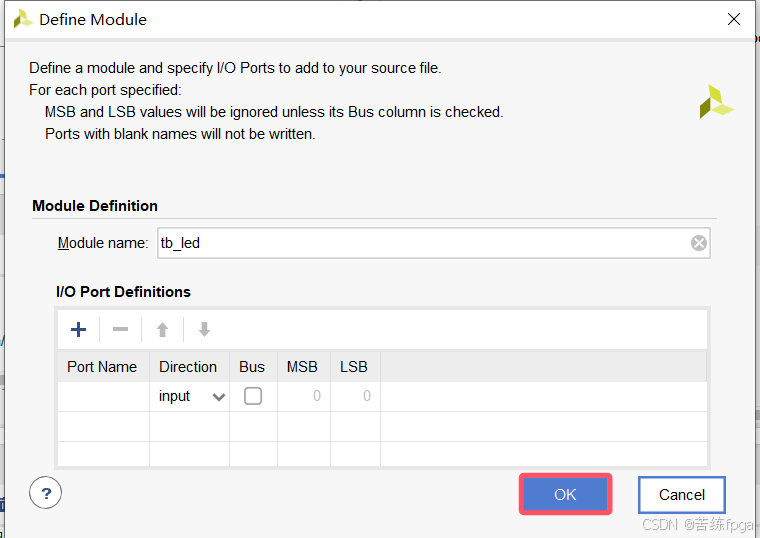

新建文件后出现下图提示框,给仿真文件命名,一般为tb_加上模块缩写

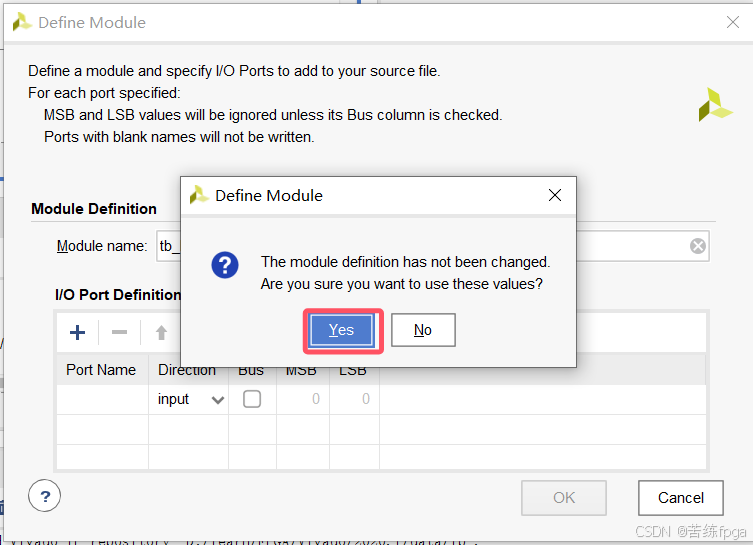

点击OK后,会出现一个新建的文件,然后点击Finish

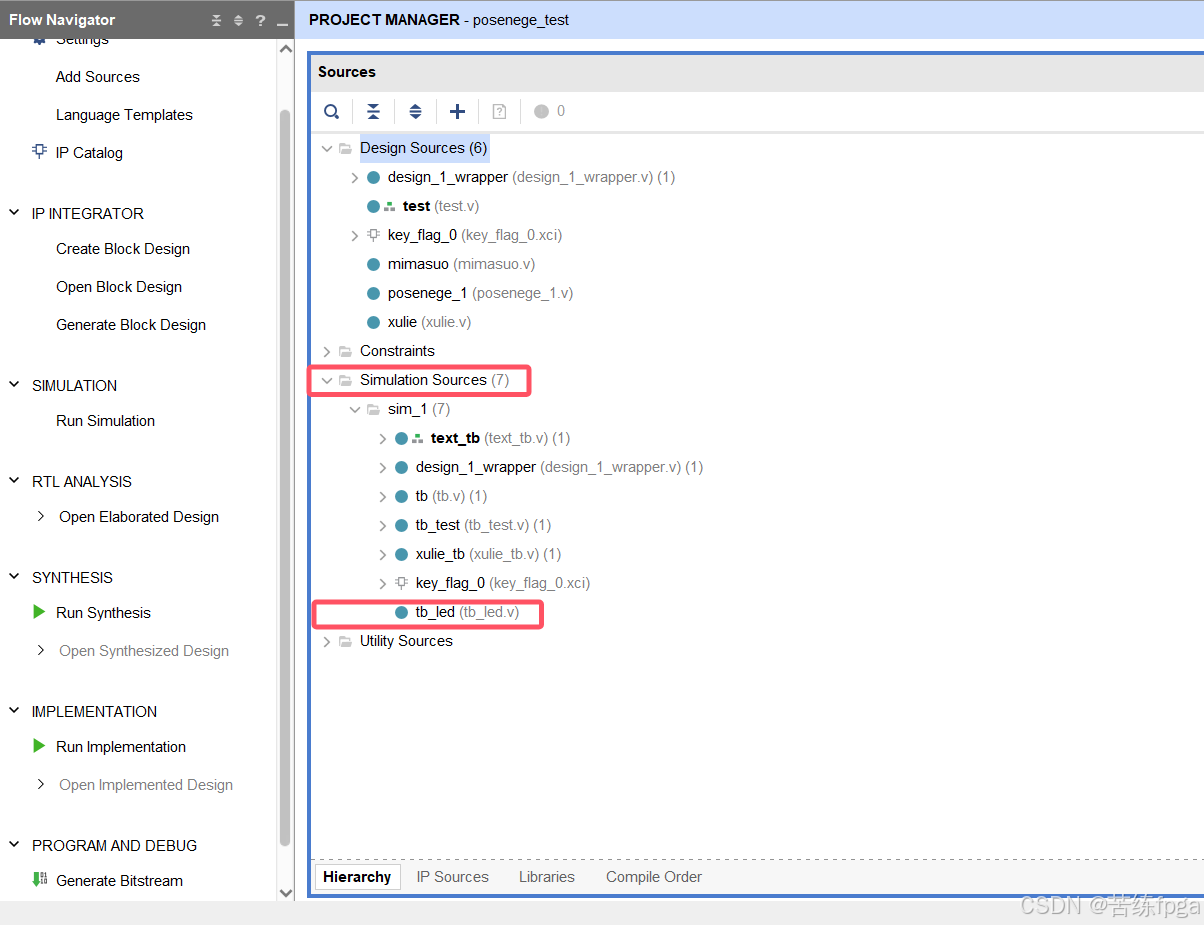

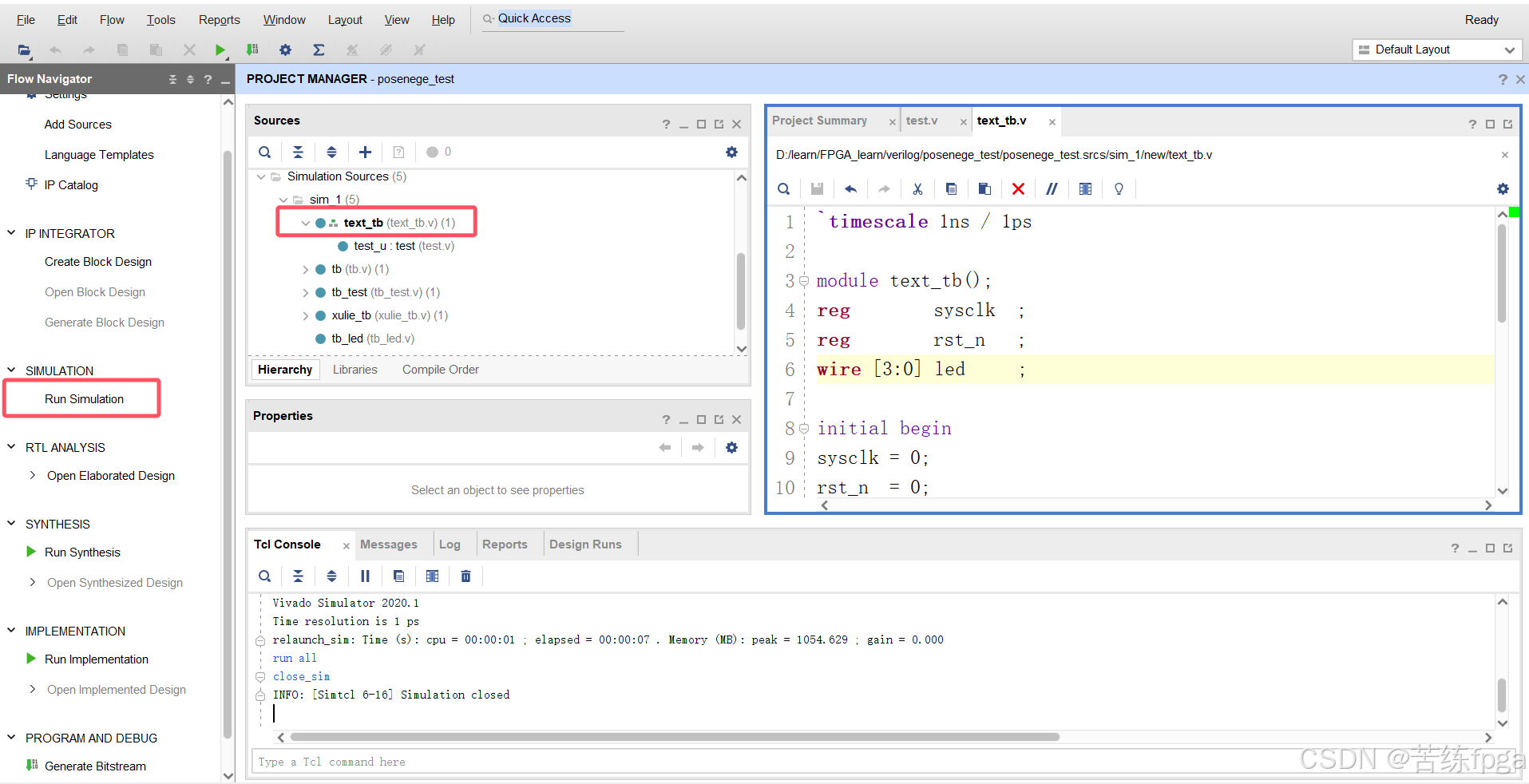

创建成功后,就可以在下拉看到自己所创建的仿真文件了

仿真代码编写:

这里的话我将以流水灯的代码来做示例去写仿真

1s流水灯verilog:

-

- module test(

- input wire sysclk ,//系统时钟

- input wire rst_n ,//复位

- output reg [3:0] led

- );

-

- parameter delay = 50_000_000;//1s内部晶振次数

- reg [26:0] cnt;//计数器,记录是否达到一秒

-

- //1s计时器——按键按下开始计时

- always @(posedge sysclk)

- if(!rst_n)

- cnt <= 0;

- else if(cnt == delay - 1)

- cnt <= 0;

- else

- cnt <= cnt + 1;

-

- //流水灯灯赋值

- always @(posedge sysclk)

- if(!rst_n)

- led <= 4'b0001;

- else if(cnt == delay - 1)

- led <= {led[0],led[3:1]};

- else

- led <= led;

-

- endmodule

仿真代码:

最顶部的`timescale 1ns / 1ps是时间布颈,1ns是时间单位,1ps是时间精度

注意:在仿真代码中,时间布颈一定不能写掉,在源文件里面可以不加时间布颈

步骤:

1.首先将需要仿真的代码例化进来

2.根据例化代码的端口去定义参数,输入类型定义为reg,输出类型定义为wire

3.使用initial关键字来进行初始化,输入类型的都需要进行赋值

4.生成时钟,有多种方法,根据自身的需求

- `timescale 1ns / 1ps//时间布颈,1ns是时间单位,1ps是时间精度

-

- module text_tb();

- reg sysclk ;//根据例化模块的端口定义,input类型定义为reg,output类型定义为wire

- reg rst_n ;

- wire [3:0] led ;

-

- initial begin //initial是初始化的意思,在其内部的代码只能执行一次

- sysclk = 0;//将时钟初始化为0

- rst_n = 0;//将复位信号初始化为0

- #101 //在过了101ns后

- rst_n = 1; //复位信号拉高,开始工作

-

- end

-

- always #10 sysclk = ~sysclk;//常见的时钟生成方法之一,每过10ns翻转一次,这样就是20ns一个周期

-

- test test_u(

- . sysclk (sysclk) ,//系统时钟

- . rst_n (rst_n ) ,//复位

- . led (led )

- );

- endmodule

时钟的生成方法:

1、关键字:always 是常见的产生时钟的方法之一 --->always #半个时钟周期 时钟翻转

例:always #10 sysclk=~sysclk;

2、关键字:forever 第二种时钟生成方式 ---->一直执行

例:initial begin

sysclk = 0;

forever begin

#10 sysclk=~sysclk;

end

end

3、关键字:repeat 第三次时钟生成方法 ----->()里头是多少,语句就执行多少次

例:initial begin

sysclk = 0;

repeat(10) begin

#10 sysclk=~sysclk;

end

end

仿真使用:

操作步骤:

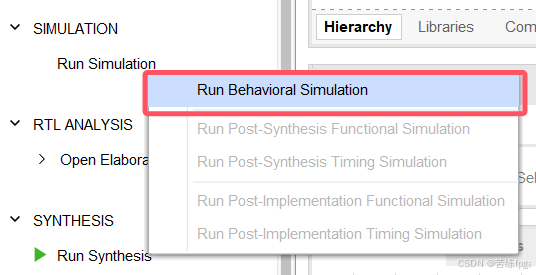

写完仿真代码后,ctrl+s保存一下,然后将自己所写的仿真代码置顶,再点击Run Sinulation

选择第一个,功能前仿真

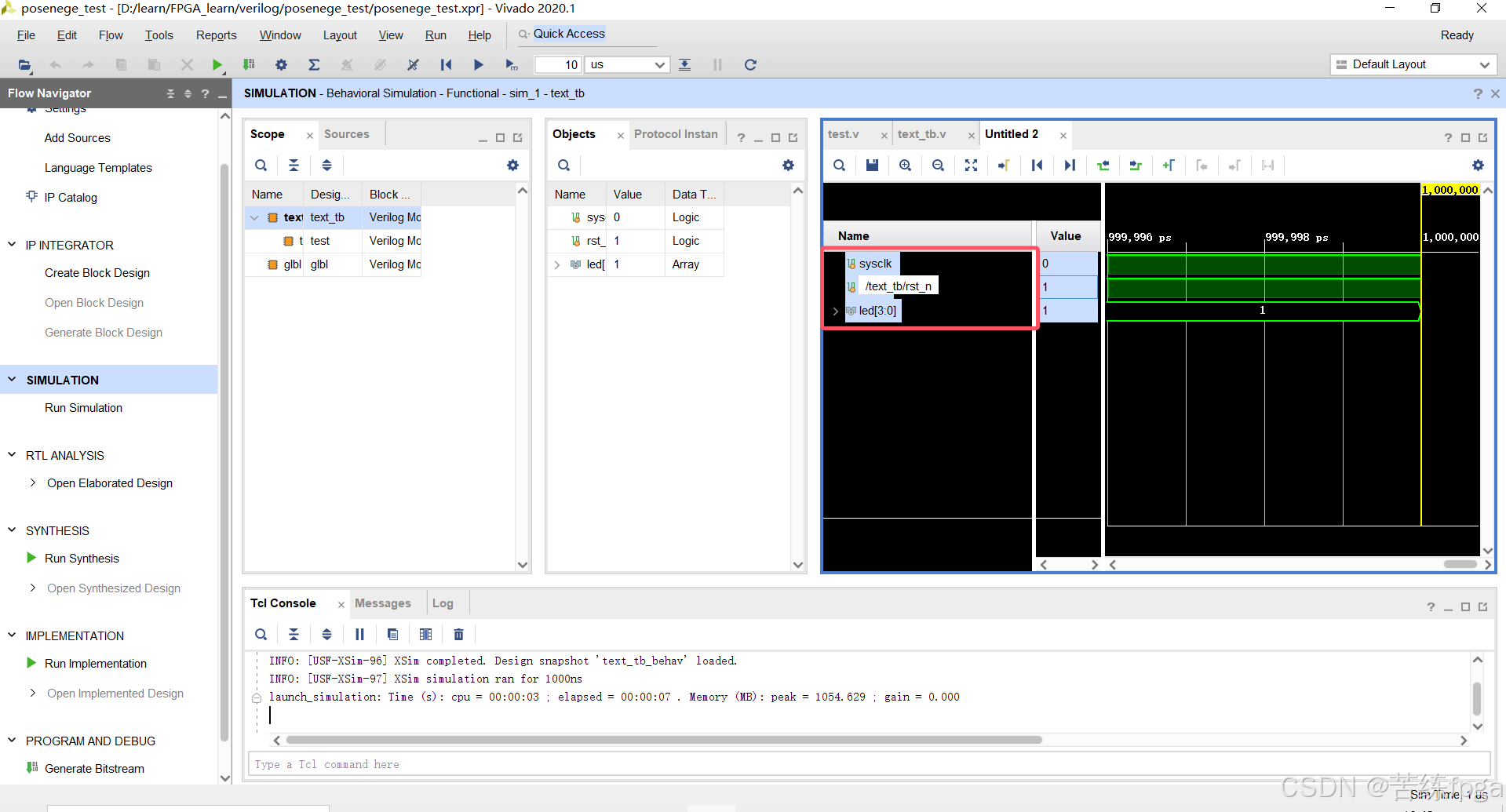

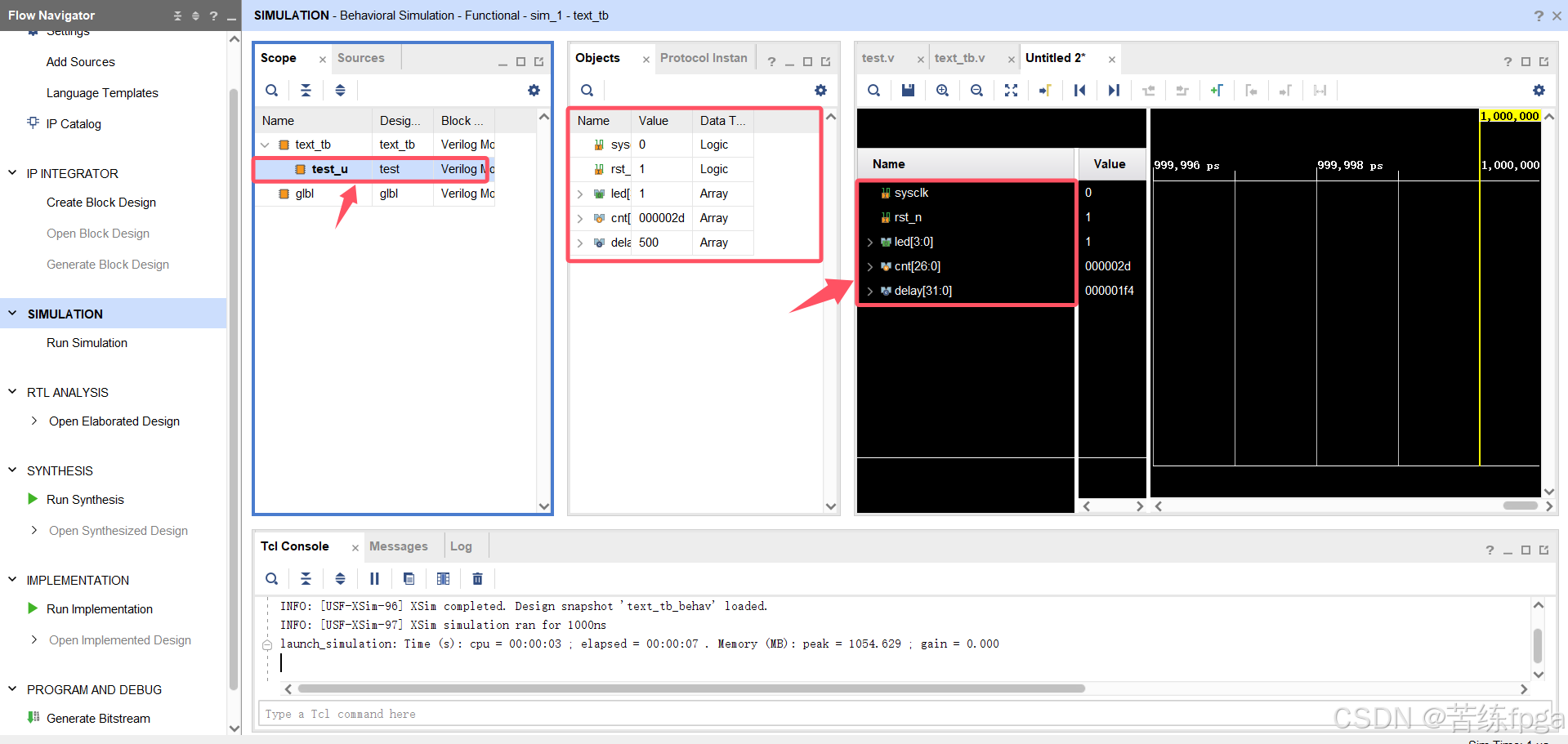

加载完后如下图所示,选中红框里的代码,ctrl+a全选,delete删除

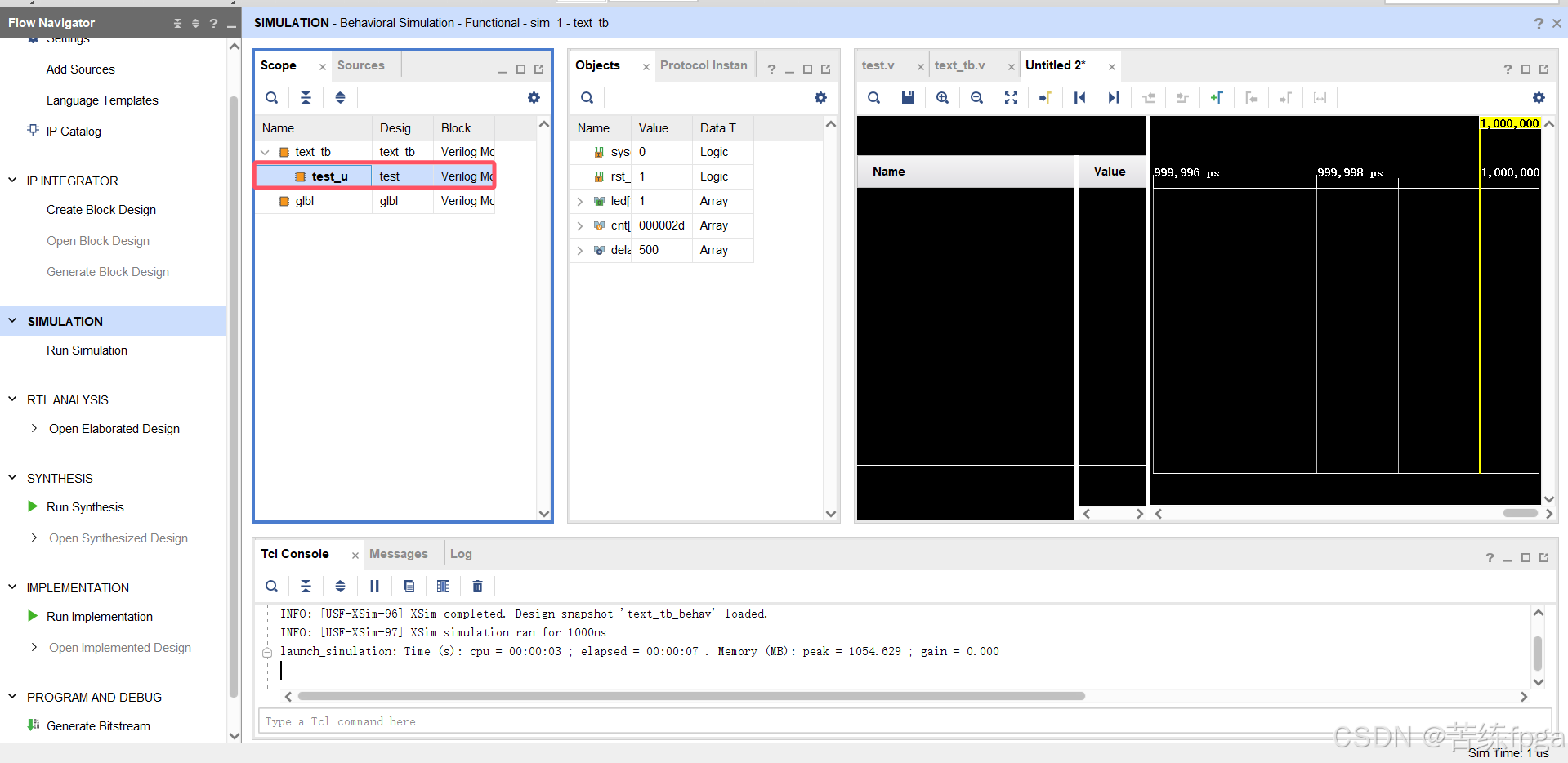

选中左边框里的文件,将其拉到刚才红框的位置

如下图所示,两个红框里的信号其实是一样的,如果不需要看这么多信号,也可以选择在左边红框里一个一个拉出所需要观察的信号

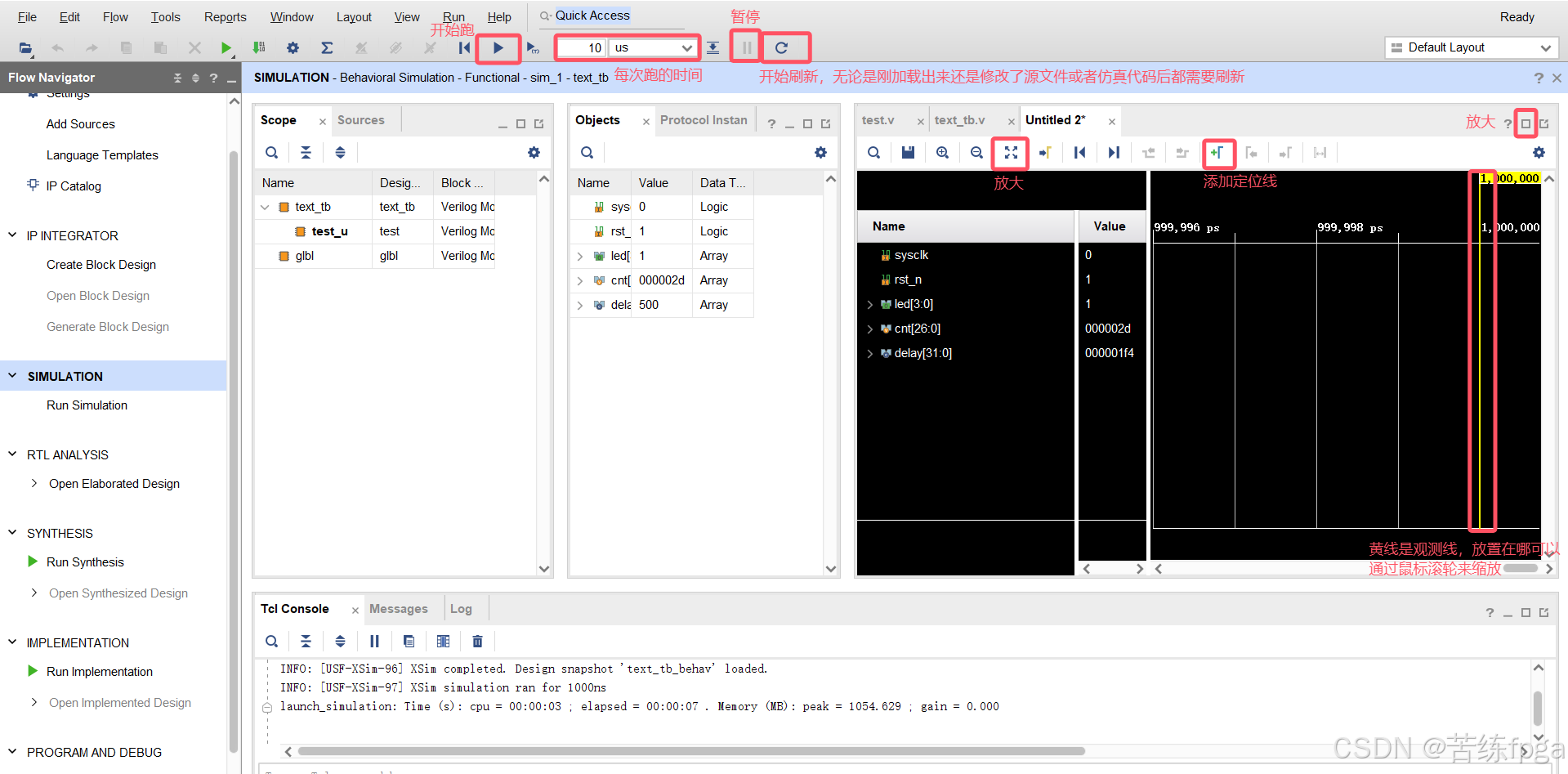

常用的操作步骤如下图所示

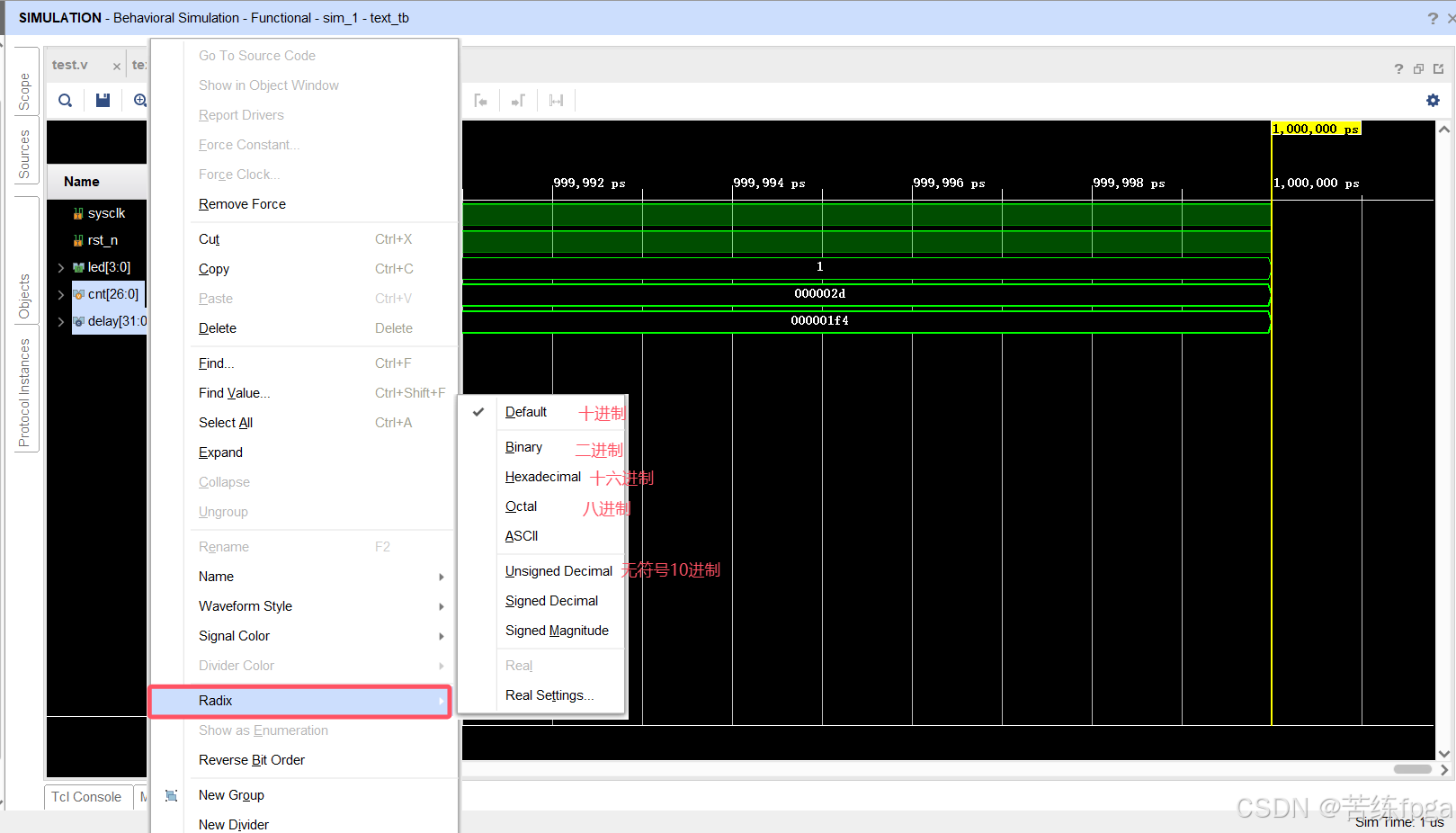

为了方便观测,可以修改进制

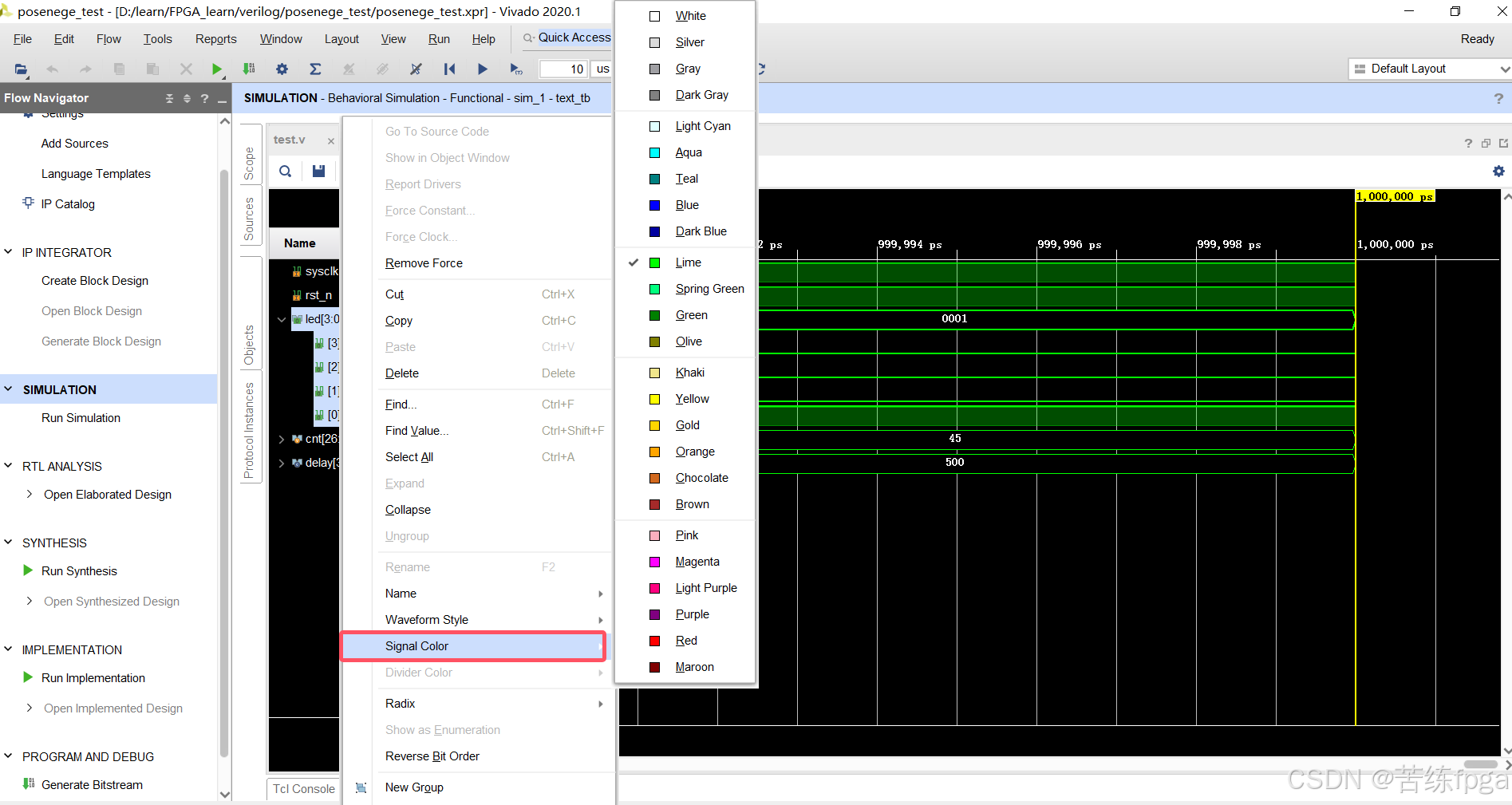

修改信号线颜色,这里需要注意的是最好不要修改成红色和蓝色

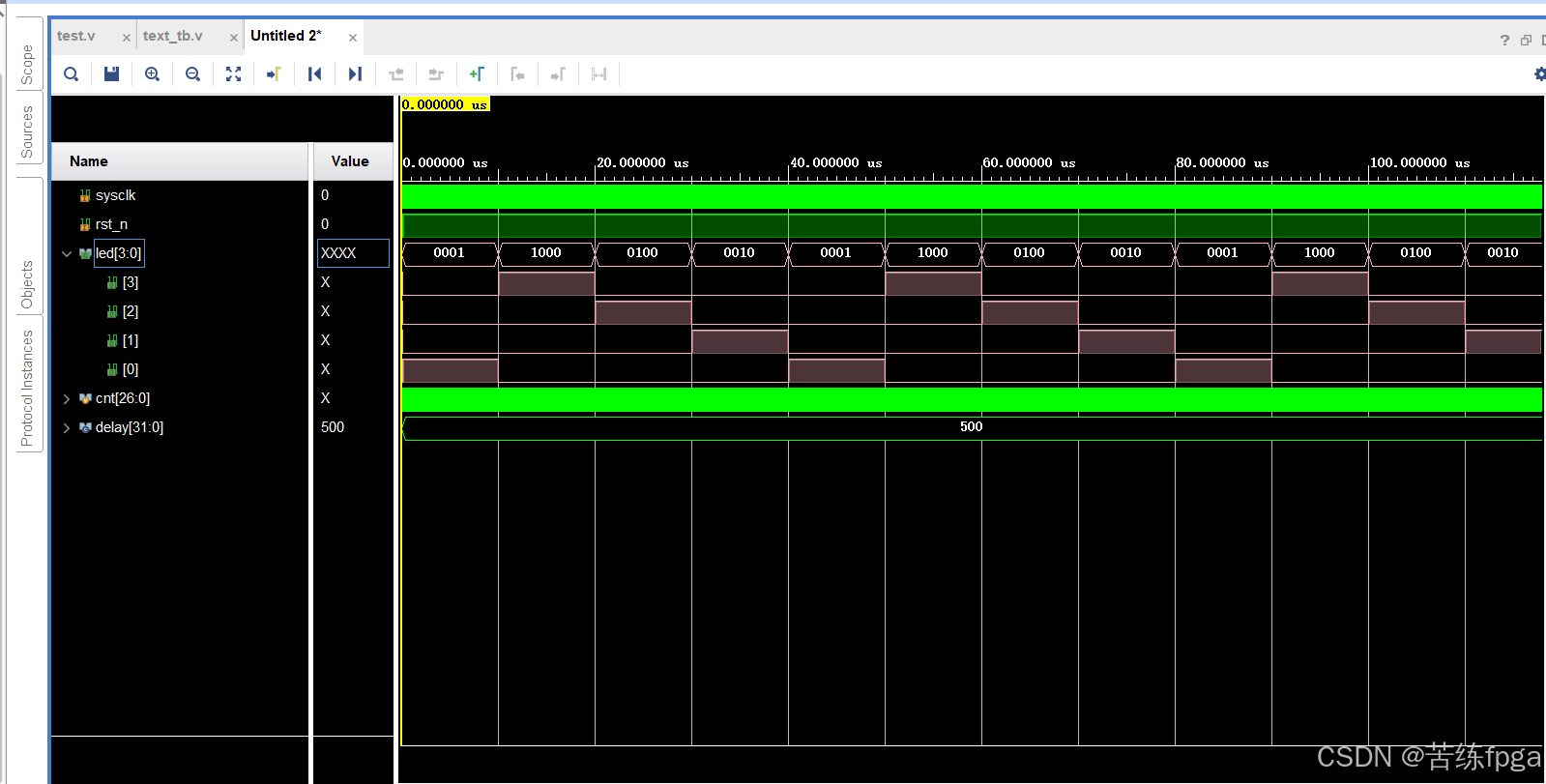

最后流水灯就像下图所示,这里我的时间是修改过后的,不然会跑很长的时间

常见时序图总结:

信号线仿出来是z(初始颜色为蓝色):

1.该信号是wire类型未赋初值,没有对其进行说明;

2.该信号线悬空,未接入(出现在例化连线时未接通)

信号线仿出来是x(初始颜色为红色):

1.仿真出来没有跑起来,不一定是错的,有可能是使用的复位方法不一样(同步复位)

2.如果跑起来依旧是x,那么就可能是reg变量没有赋值,也可能是信号位宽不够;

注意事项:在时序分析中,组合逻辑比时序逻辑要提前一个时钟周期

总结:

本次的话主要是介绍了Simulation的使用方法,以及一些常见问题的注意事项等。掌握仿真后就可以在不上板的情况下去观测试代码的逻辑功能是否能实现,例如什么UART,IIC等协议也可以通过仿真去进行模拟。有错的地方希望能够帮忙指正,谢谢!

评论记录:

回复评论: