一.verilog概述

- Verilog全称是Verilog Hardware Description Language(Verilog硬件描述语言),缩写为Verilog HDL,简称Verilog。

- Verilog是一种功能强大且灵活的硬件描述语言,它允许设计者以代码形式来描述数字系统和电路的结构和行为。通过学习和掌握Verilog,设计者可以更加高效地设计和验证数字电路,提高设计质量和效率。

二.与其他语言的比较

- 与C和Java等软件编程语言相比,Verilog的语法和编程概念有所不同。

- Verilog用于描述数字电路和数字系统,而C和Java则用于编写在计算机上运行的软件程序。

- Verilog描述了线、寄存器和逻辑门的属性,而C和Java则定义了变量、函数和控制循环。

- Verilog代码被编译成可以在物理电路或FPGA中实现的硬件配置,而C和Java代码被编译成可以由计算机处理器直接执行的机器代码。

三.verilog的基础知识

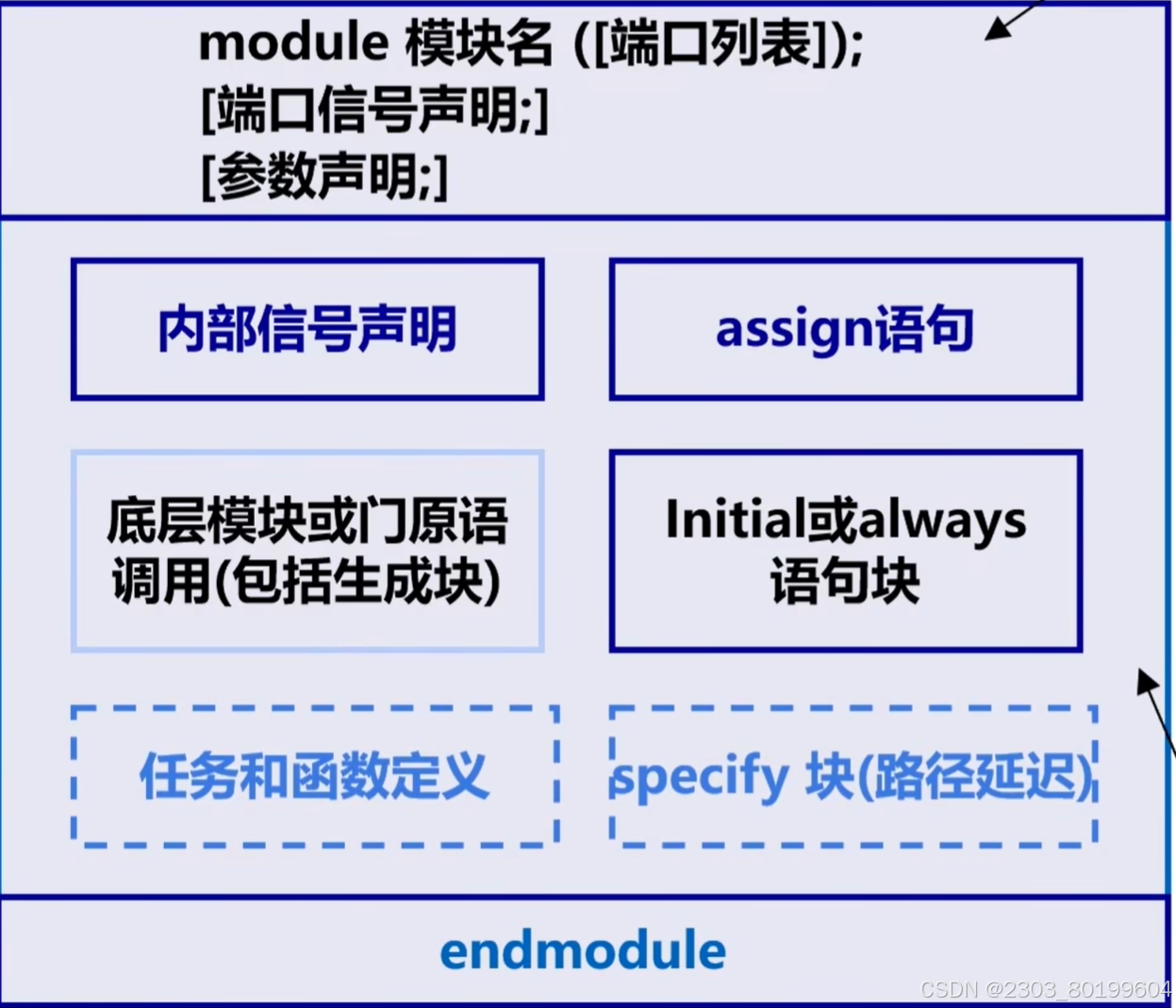

3.1模块结构

一般使用assign.always语句 ,module和endmoudule是必不可少的,下面来讲讲这两种常用的语句。

端口定义:

输入端口input

输出端口output

双向端口inout

3.1.1常量

无符号数格式:[换算为二进制后位宽的总长度]['][数值进制符号][与数值进制符号对应的数值]

有符号数格式:[换算为二进制后位宽的总长度]['][s数值进制符号][与数值进制符号对应的数值]

8'd171: 位宽是8bit,十进制的171。

[数值进制符号]中如果是[h]则表示十六进制,如果是[o]则表示八进制,如果是[b]则表示二进制,如果是[d]则表示十进制。

[换算为二进制后位宽的总长度]:可有可无,verilog 会为常量自动匹配合适的位宽。

当总位宽大于实际位宽,则自动在左边补0,总位宽小于实际位宽,则自动截断左边超出的位数。

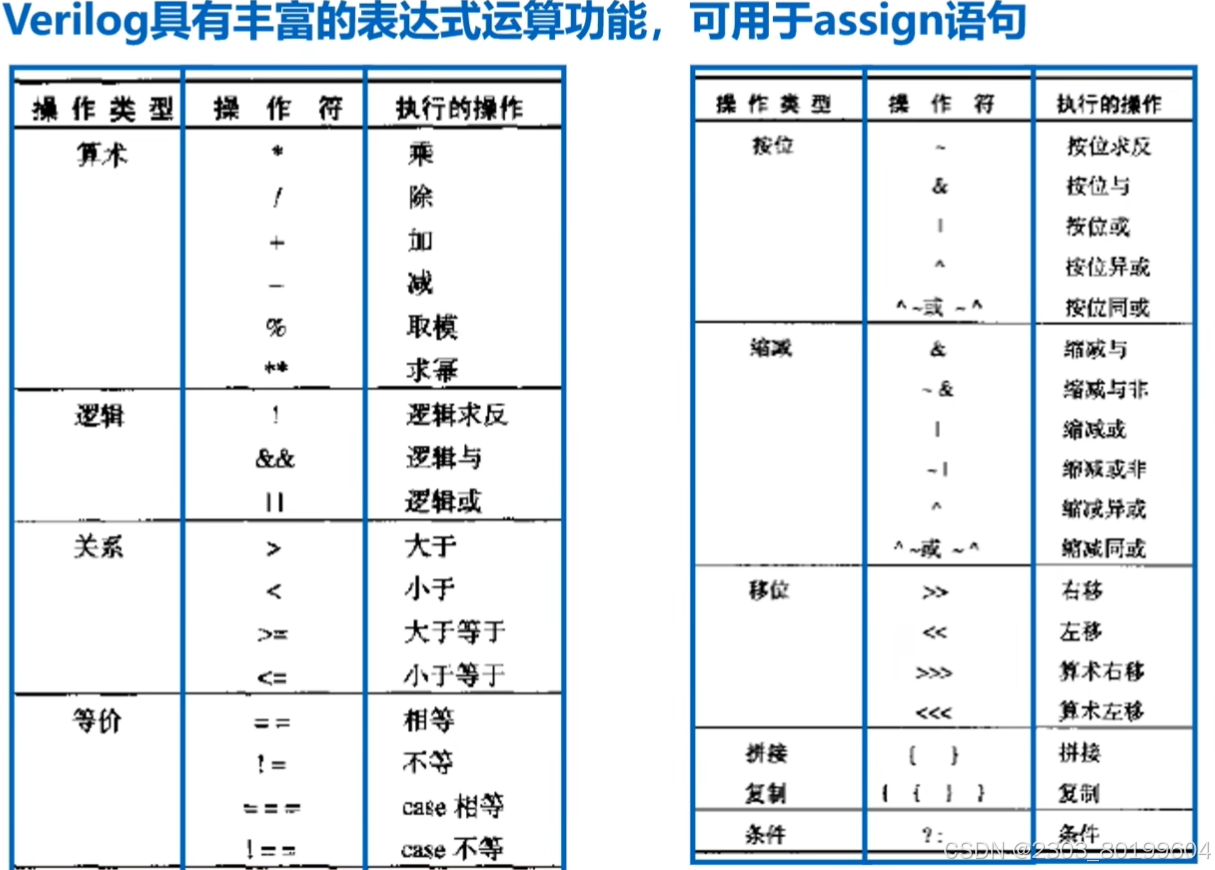

3.2 assign语句

又称为连续赋值语句

格式:assign 赋值目标=表达式,assign赋值目标必须为wire数据类型,一般不做说明默认为wire型,reg型需要手动定义。主要说一些比较陌生的符号。

3.2.1算术型

强调一个求幂运算符**,其余的操作符与c语言类似。

Y=2**3 结果为8

3.2.2逻辑值

0: 逻辑低电平,条件为假

1: 逻辑高电平,条件为真

z: 高阻态,无驱动

x: 未知逻辑电平

3.2.3等价

强调一下==和===的区别 ,==一般是用于比较两个操作数,但是对于比较包含未定义的值(x或z)时,会返回不确定的结果。===是三等号操作符,不仅比较操作数的值,还比较值位和未知位x

3.2.4拼接复制

{ }拼接 格式:{ 操作数1,操作数2...}

{ { } }复制拼接 格式:{n{操作数1,操作数2 }} 例如:Y={{4{2'b01}},2'b11} 结果为0101010111

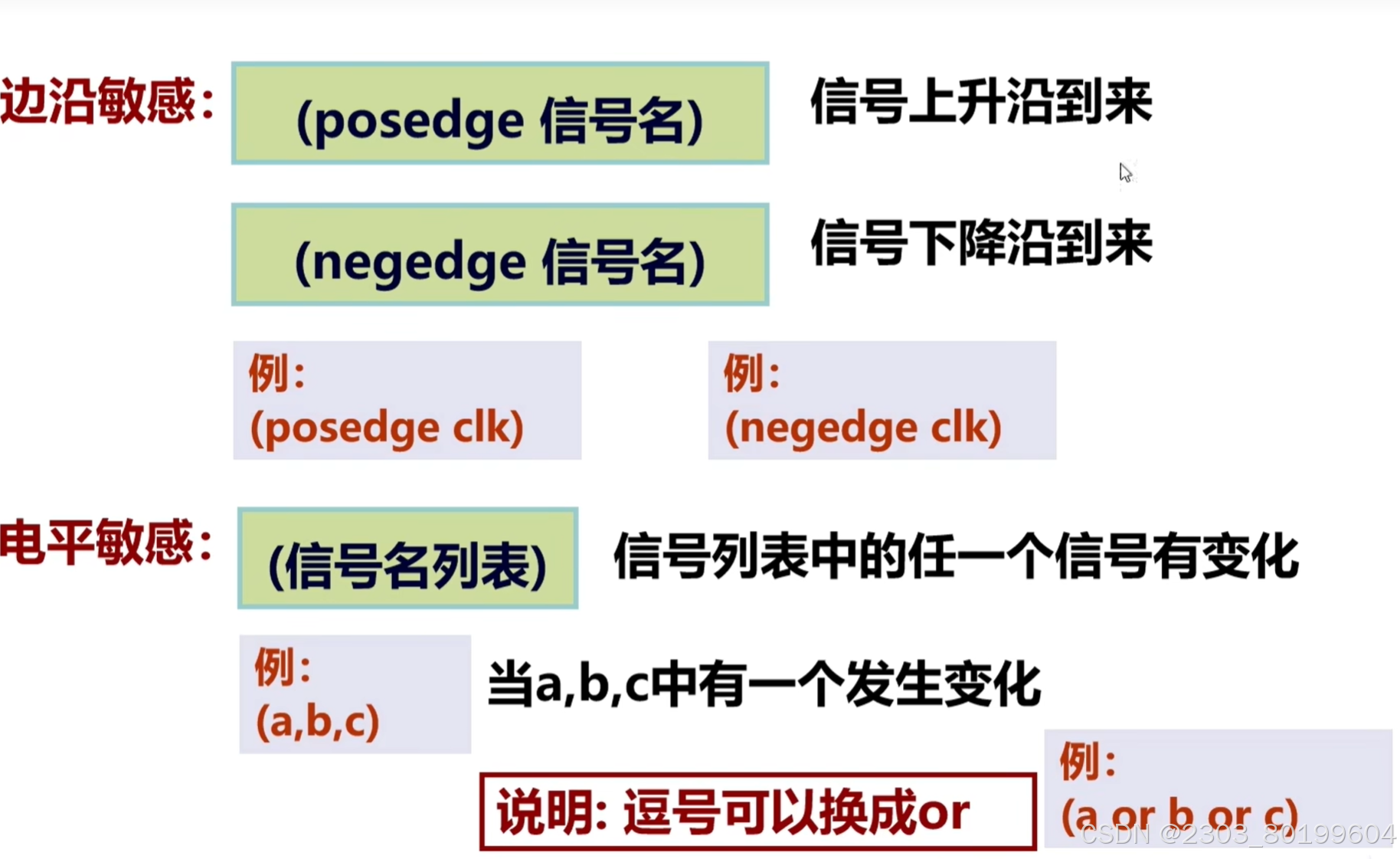

3.3 always语句

又成为过程赋值语句

格式:always @(敏感信号条件)

各类顺序语句;

赋值目标必须是reg型,敏感条件分为1.边沿敏感2.电平敏感,触发条件列表中的多个条件之间采用“or”来连接。下面是具体案例

3.3.1门原语调用

格式:门原语名 实例名(端口连接)

其中实例名一般可以省略,端口连接采用顺序法输出在前,输入在后

门原语: and与 or或 xor异或

nand与非 nor或非非 xnor同或

3.3.2 assign和always主要区别:

assign总是处于激活状态,只要操作数一变化就马上进行计算和赋值。always语句块挂起,直到激活该过程,才会进行计算和赋值,未激活,改变操作数无效。assign赋值目标为wire型,always赋值目标为reg型。

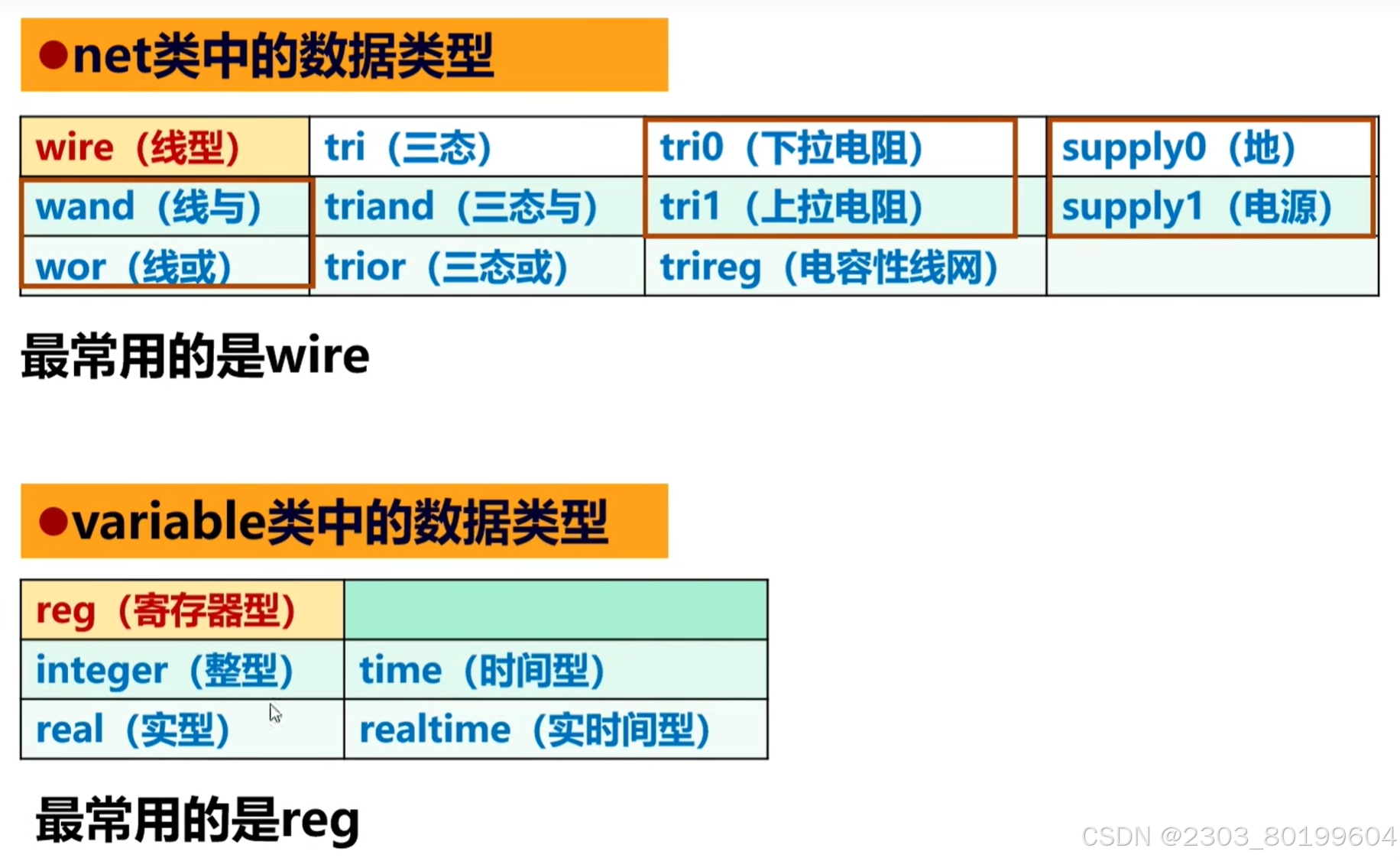

3.4数据类型

分为两大类:线网类(net类),变量类(variable类)。

net型一般用于连续赋值的赋值目标或门原语的输出,仿真时不需要分配内存空间,variable用于过程赋值的赋值目标且仿真时需要分配内存空间。

对于端口信号来说input inout必须定义成net型,output可以是net也可以是variable,取决于如何对它赋值。

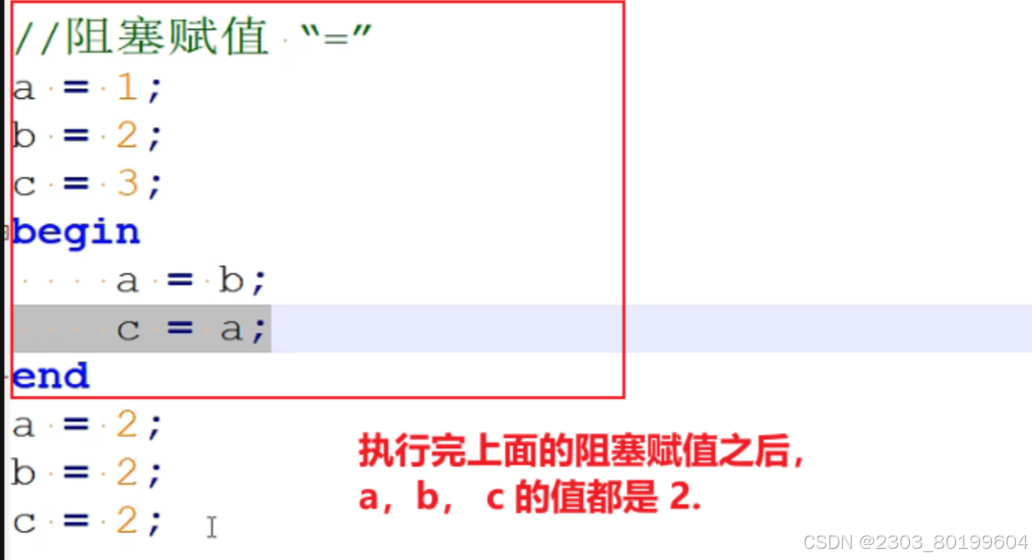

3.5赋值方式

阻塞型赋值 =

阻塞赋值可以理解为顺序执行,也就是说第一句语句执行完毕之后, 才会执行第二句语句。声明 3 个变量,a 的值是 1,b 的值是2,c 的值是 3.

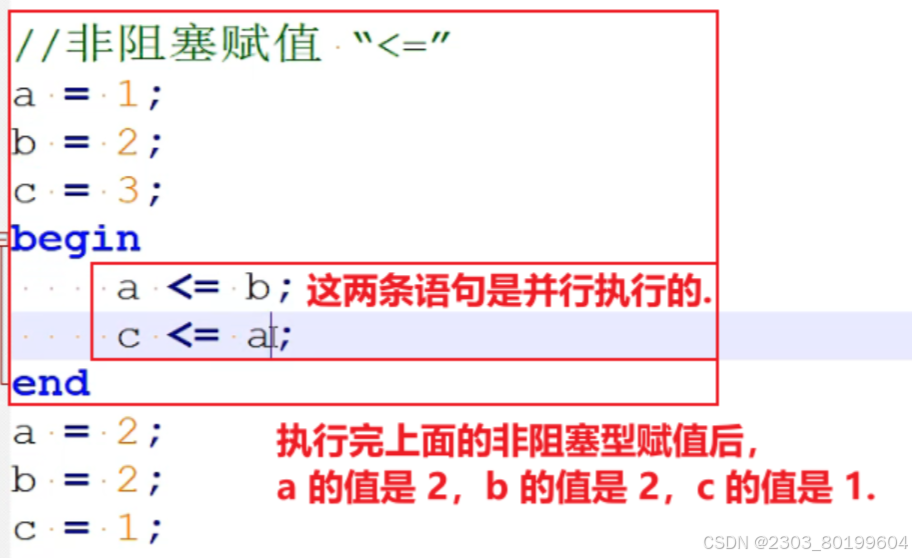

非阻塞型赋值<=

非阻塞型赋值语句是并行执行的。即在同一时刻,多条语句是同时执行的。

声明 3 个变量,a 的值是 1,b 的值是2,c 的值是 3.

b 的值目前是 2,a 的值目前是 1. 在同一时刻,将 b 的值赋值给 a,将 a 的值赋值给 c.

3.6条件语句

if-else语句

与c语言相似,这里就不强调了

case语句(类似于c语言中switch)

格式:case(条件)

值1:语句1;

值2:语句2;

值n:语句n;

default:语句n+1;

endcase

3.6其他规定

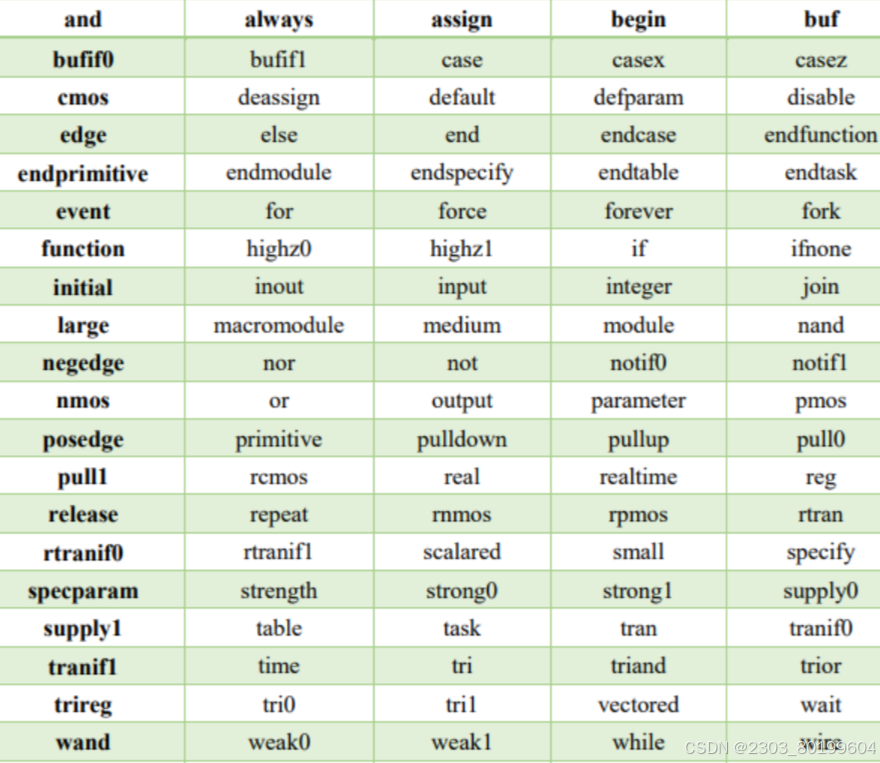

3.6.1关键字

Verilog HDL中所有的关键字都是小写的。

3.6.2标识符

标识符用来命名信号、模块、参数等,它可以是任意一组字母、数字、$符号和_(下划线)符号的组合。标识符中字母区分大小写,且第一个字必须是字母或下划线。

3.6.3文件取名和存盘

verilog的文件拓展名为.v,verilog不要求文件名和模块名一致,但QUartII要求一致

总结:

学习新的语言还是需要多敲代码,学的还只是边角料远远不够用

评论记录:

回复评论: