目录

前言

D触发器虽然基础,但很重要,扎实地掌握对于硬件电路学习者必不可少,传统地认识D触发器的过程大概是给出电路图,分析电路图,写出真值表,然后硬件语言描述,功能仿真,用综合工具综合出电路。

这对于直观的认识D触发器还是有点儿困难,个人觉得这种简单的电路,用Verilog HDL硬件语言描述可以直观地认识到它的功能,然后在观察其仿真波形,之后在用综合工具综合出相应的电路图来查看,再对其进行分析,会更符合至少是个人的认识规律。

分析电路原理图虽然不难,但是这个过程还是很繁琐,这里不打算进行这种分析。

下面直接给出1位D触发器的Verilog HDL硬件语言描述和测试文件;(包括异步清零和同步复位)

硬件语言描述

下面的硬件语言描述的是一个1为的D触发器,其功能为,当时钟上升沿到来时,输入信号d传输到输出端q,清零信号在always的敏感列表中,使得该触发器还具有异步清零的功能,rst为同步复位信号。

- //1位D触发器Verilog HDL程序代码

-

- module dff(clk,clr,rst,d,q);

- input clk;

- input clr,rst;

- input d;

- output q;

- reg q;

-

- always@(posedge clk or posedge clr) //敏感源为时钟上升沿或清零信号的上升沿(异步清零)

- begin

- if(clr == 1'b1) //清零信号有效时(高电平),输出清零

- q <= 1'b0;

- else if(rst == 1'b1) //复位信号有效时(高电平),输出置1(同步置1)

- q <= 1'b1;

- else //二者都无效时,输出保持当前状态

- q <= d;

- end

-

- endmodule

测试文件

- `timescale 1ns/1ps

- module dff_tb;

-

- wire q;

- reg clk,clr,rst,d;

-

- //时钟信号

- always

- begin

- # 10 clk = ~clk;

- end

-

- //初始化

- initial

- begin

- clk = 1'b0;

- clr = 1'b0;

- rst = 1'b0;

- d =1'b0;

- #10 rst = 1'b1; //10ns后复位信号有效,此刻应该输出置1

- #10 clr = 1'b1; d = 1'b1; //又过10ns,清零信号有效,且复位信号也继续有效,但清零信号优先级高,所以,此刻输出应该清零

- #10 clr = 1'b0; rst = 1'b0; //又过了10ns,此刻复位和清零信号均无效,此刻输出应该保持当且输入的状态,也就是高电平

- #20 d = 1'b0;

- #20 d = 1'b1;

- end

- //实例化

- dff u1(.clk(clk), .clr(clr), .rst(rst), .d(d), .q(q));

- endmodule

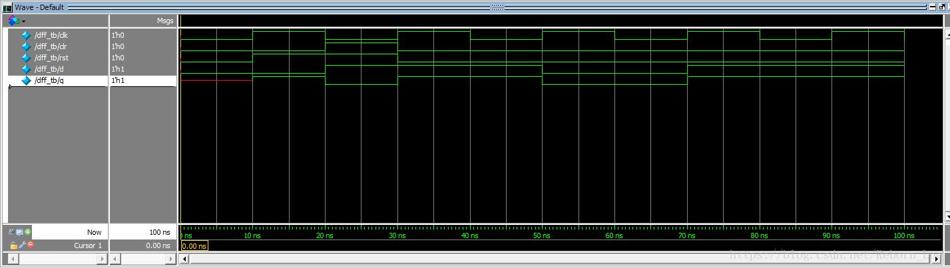

仿真图

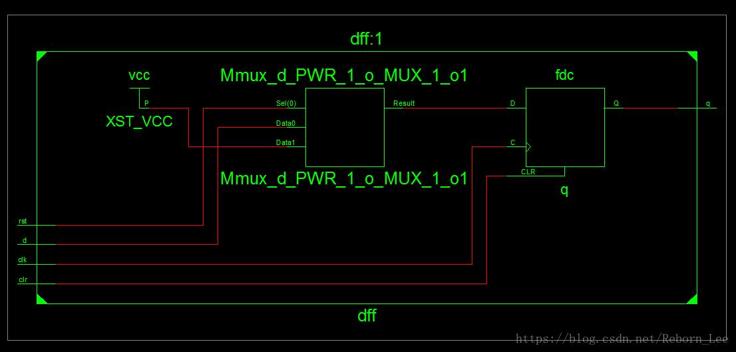

综合工具综合后的原理图

简单的分析下这个电路,与rst相连的是一个二选一的选择器的选择端,当rst为1的时候,也就是高电平时候,选择Data1有效,此刻选择器的输出结果result为1,选择器的输出又接到D触发器的数据输入端,这就意味着时钟上升沿到来时,结果为1。这不就是说明rst高电平有效,有效时,置1。

当rst为0时,选择器的输入Data0被选中作为D触发器的输入,这不就意味着rst无效时,D触发器的输出取决于输入信号的当前状态吗!

当然,优先级别更高的是clr,也就是说当clr有效时,输出清零,而不管rst以及输入的值是什么。这点在硬件语言描述中有体现出来,这里综合出来的电路也体现出来了。

综合介绍D触发器

维基百科介绍:

The D flip-flop captures the value of the D-input at a definite portion of the clock cycle (such as the rising edge of the clock). That captured value becomes the Q output. At other times, the output Q does not change.

这段话来自于维基百科。来说说这句经典的话是什么意思吧。

D触发器在时钟周期的某一部分(例如时钟的上升沿)捕获D输入的值。 捕获的值成为Q输出。 在其他时候,输出Q不会改变。

它表达了一个十分普遍的意思,就是D触发器通常在时钟上升沿时,此刻会捕获D输入的值,然后保持这一值不变,直到下一个上升沿到来时,重新捕获D输入的值。

其他来源(课本):

在数字电路或数字系统中,触发器是时序逻辑电路用来存储1位二进制信息的基本单元电路,它靠双稳态电路来保存信息,具有存储记忆功能。触发器属于边沿敏感的存储器件,数据存储的动作由时钟信号的上升沿或下降沿进行同步。

所存储的数值取决于时钟在其有效沿(上升沿或下降沿)发生跳变时数据输入端当时的数据,在其他所有时间上数据值及其跳变均被忽略,输出保持跳变沿时刻捕获的值。

注意:

D触发器是一种最简单的触发器,它在每个时钟的有效边沿存储输入端的当前值,该值与当前存储的数据值无关。虽然在clk的两个有效边沿之间的D数据的跳变,但是,在clk有效沿到来之前,D必须稳定足够的时间,否则器件可能工作不正常。

8位的D触发器

本想到此结束的,但还是附送一个礼包吧。

上面仿真的是一个1位的D触发器,下面用硬件语言描述一个简单的8位D触发器,信号的输出q由clk的上升沿和输入信号d决定,当时钟上升沿到来时,输入端信号d传输到输出端q,不含清零和复位信号。(清零和复位信号,随便一加就好了,这里为了通用性不加了。)

Verilog HDL程序设计

- //1位D触发器Verilog HDL程序代码

-

- module dff(clk,d,q);

- input clk;

- input[7:0] d;

- output[7:0] q;

- reg [7:0]q;

-

- always@(posedge clk) //敏感源为时钟上升沿

- begin

- q <= d;

- end

-

- endmodule

测试文件:

- `timescale 1ns/1ps

- module dff_tb;

-

- wire[7:0] q;

- reg clk;

- reg[7:0] d;

-

- //时钟信号

- always

- begin

- # 10 clk = ~clk;

- end

-

- //初始化

- initial

- begin

- clk = 1'b0;

- d =8'b00000000;

- #10 d = 8'b00000011;

- #10 d = 8'b00000000;

- #10 d = 8'b00000111;

- #40 d = 8'b00001111;

-

- end

-

- //实例化

- dff u1(.clk(clk), .d(d), .q(q));

-

- endmodule

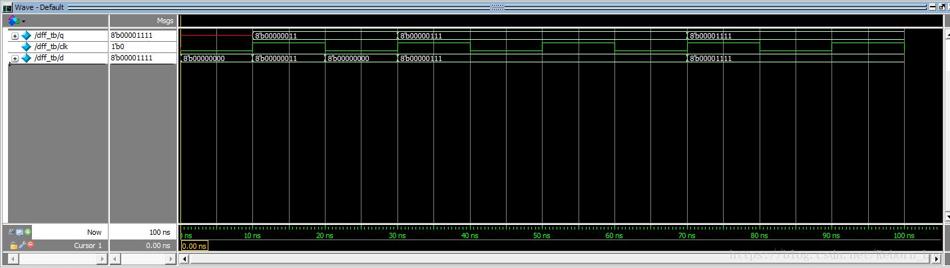

仿真波形:

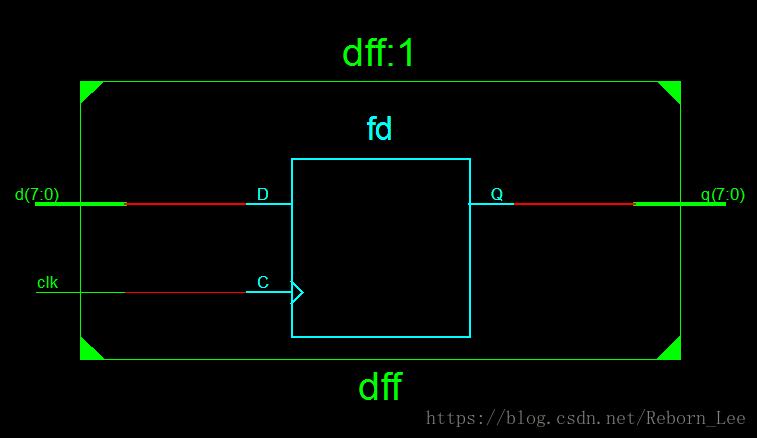

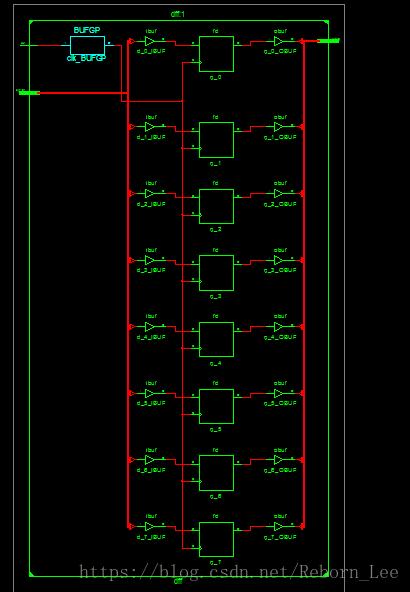

综合工具综合后的电路:

内部电路图(Technology Schematic)为:

可见,它是由8个1位的D触发器组成的。

评论记录:

回复评论: