主要更新:

MicroBlaze™ V 软处理器(基于 RISC V 开源 ISA)的通用访问

面向 Versal 器件的 QoR (FMAX) 增强功能

优化了整个 SLR 边界的时钟与 P&R(面向 multi-SLR Versal 器件)

物理优化过程中由用户控制的重新定时

用户控制的时钟树选择可实现时钟偏差的最小化

Dynamic Function eXchange (DFX) 强化

增强了 DFX 设计的报告,辅助设计收敛。

为串列配置以及针对 Versal SSIT 器件的 DFX 增加了支持,可满足 PCIe® 时序要求

Power Design Manager

增加了对 Zynq™ UltraScale+™ RFSoC 器件的支持

显示分类片上功率和静态电流的图表

能够将 PDM 表复制并导出到电子表格,以便快速共享信息

重点关注

本次更新重点关注《MicroBlaze™ V 软处理器》

Reference Guide

https://docs.amd.com/r/en-US/ug1629-microblaze-v-user-guide/Introduction

AMD MicroBlaze™ V 处理器是一款面向 AMD 自适应 SoC 和 FPGA 的软核 RISC-V 处理器 IP。MicroBlaze V 处理器基于 32 位 RISC-V 指令集架构 (ISA)。它允许开发人员利用开源 RISC-V 软件生态系统,不仅硬件与经典 MicroBlaze 处理器兼容,而且完全集成在 Vivado™ 和 Vitis™ 工具设计流程中。MicroBlaze V 处理器经过精心设计,实现了高度的模块化,具有适合嵌入式系统应用的可配置架构。

开发人员可将 MicroBlaze V 处理器对准由 Vivado 设计套件提供支持的任何 AMD 自适应 SoC 或 FPGA 器件,无需额外的费用。

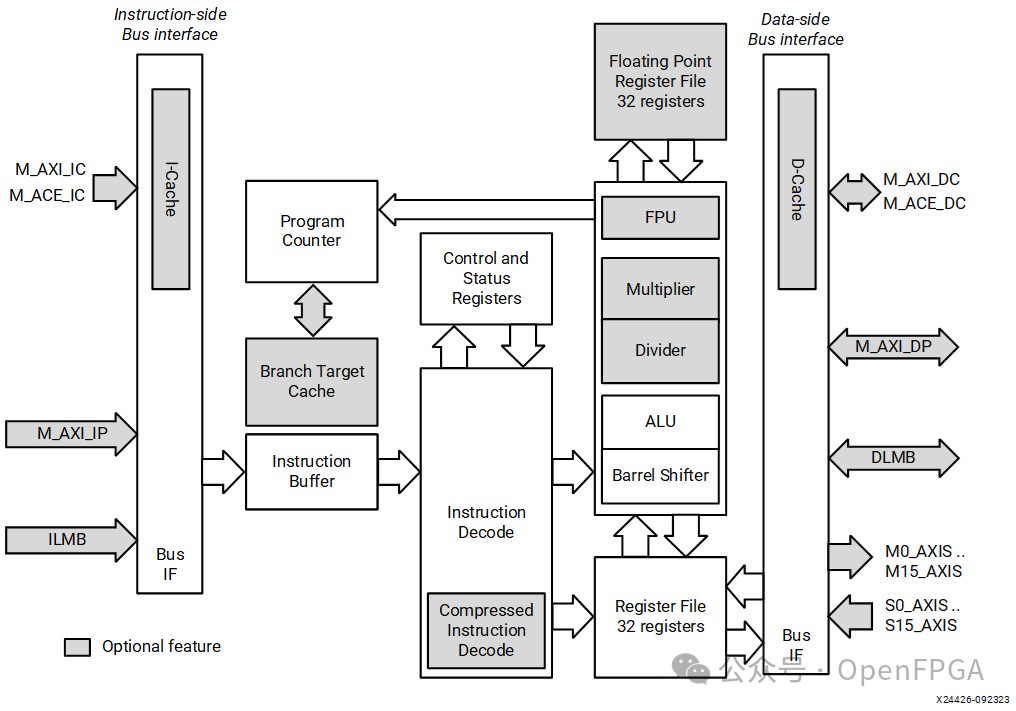

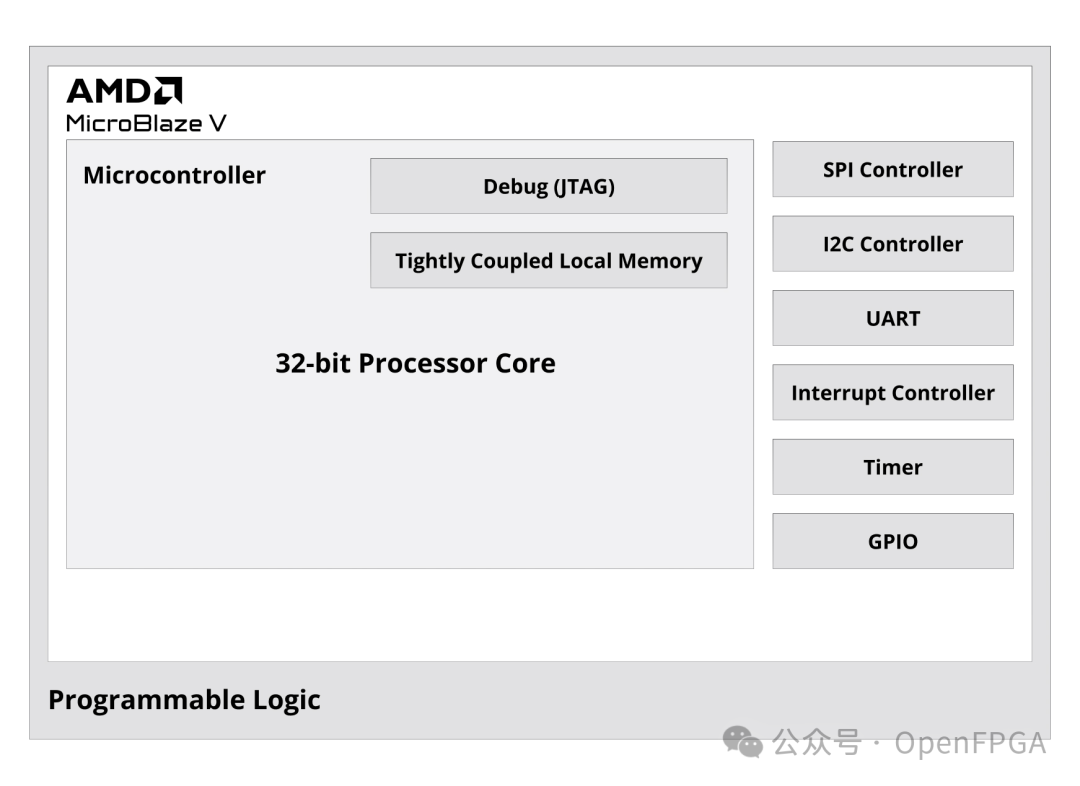

架构

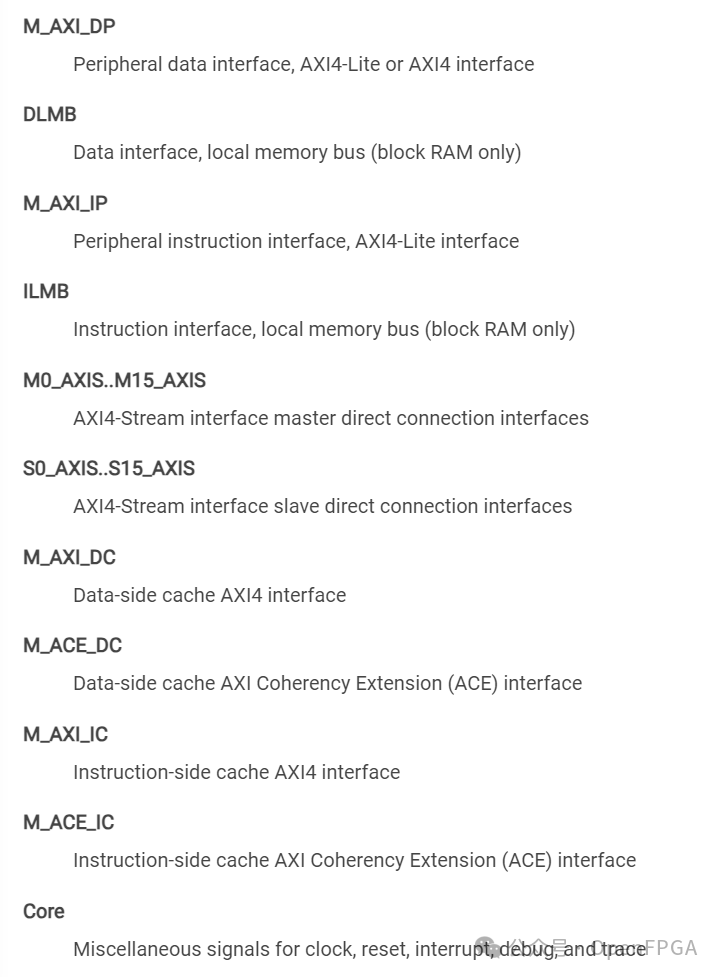

扩展接口

主要外设

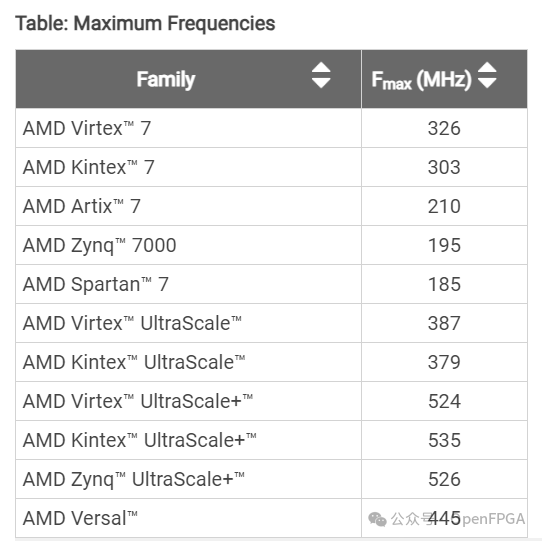

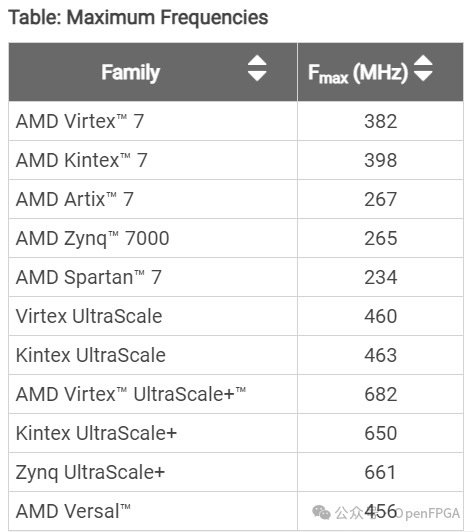

性能

对比原版本MB:

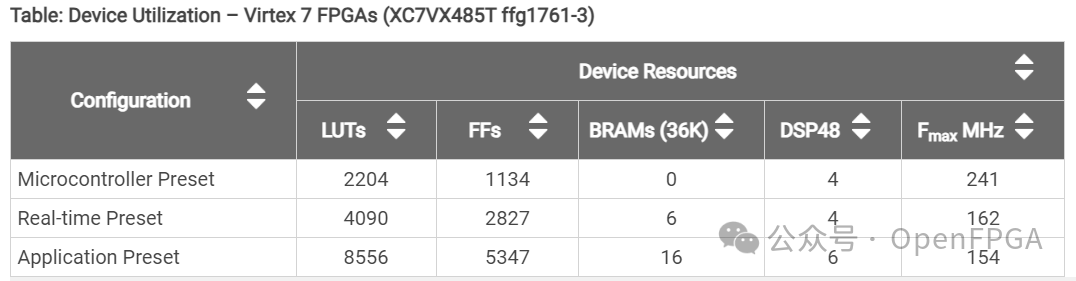

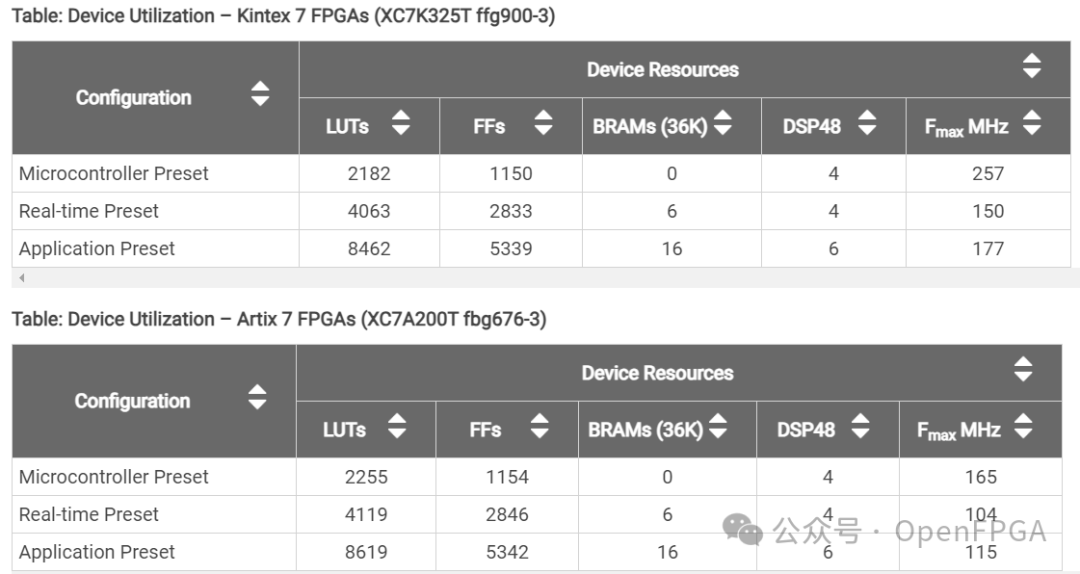

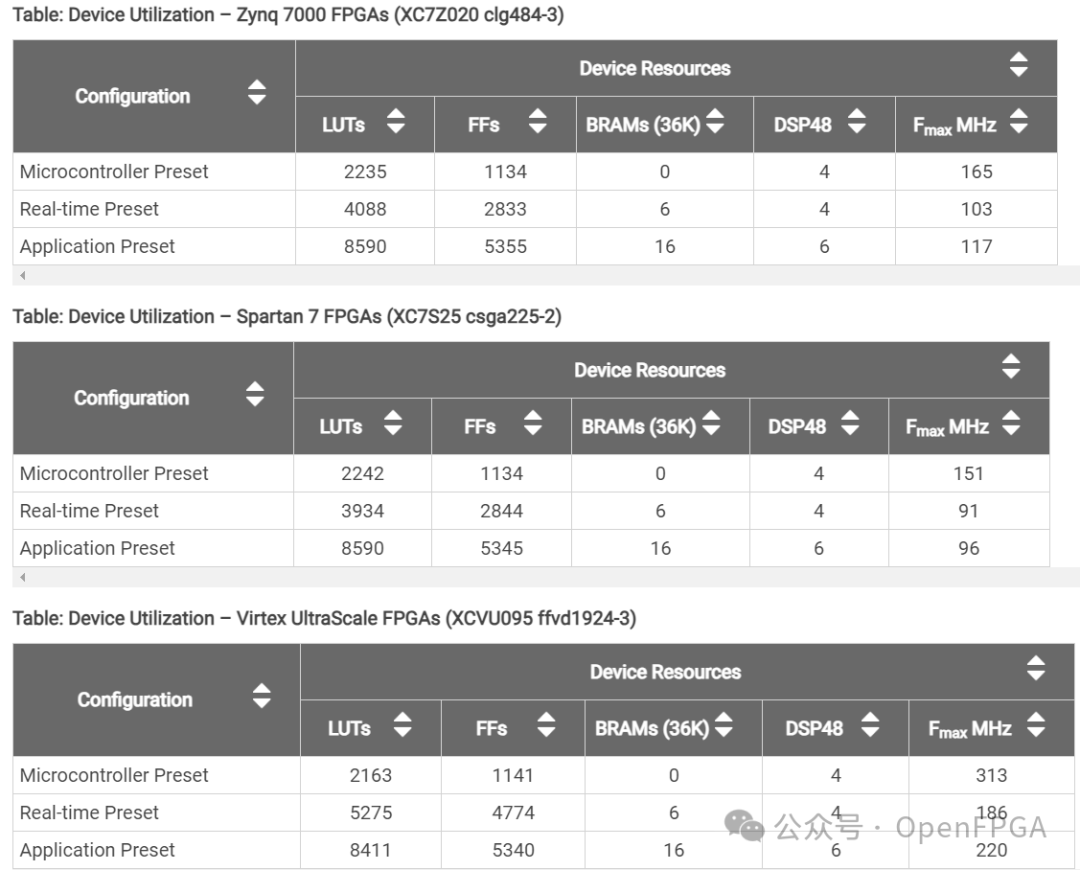

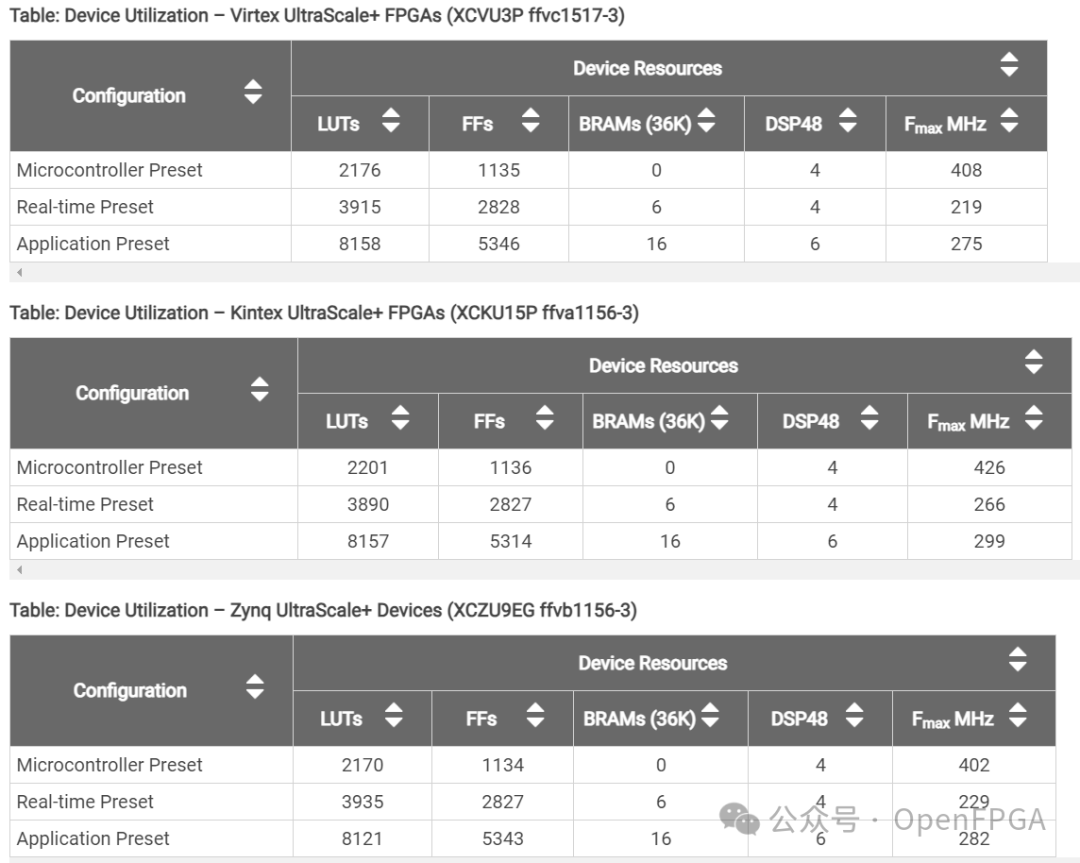

资源

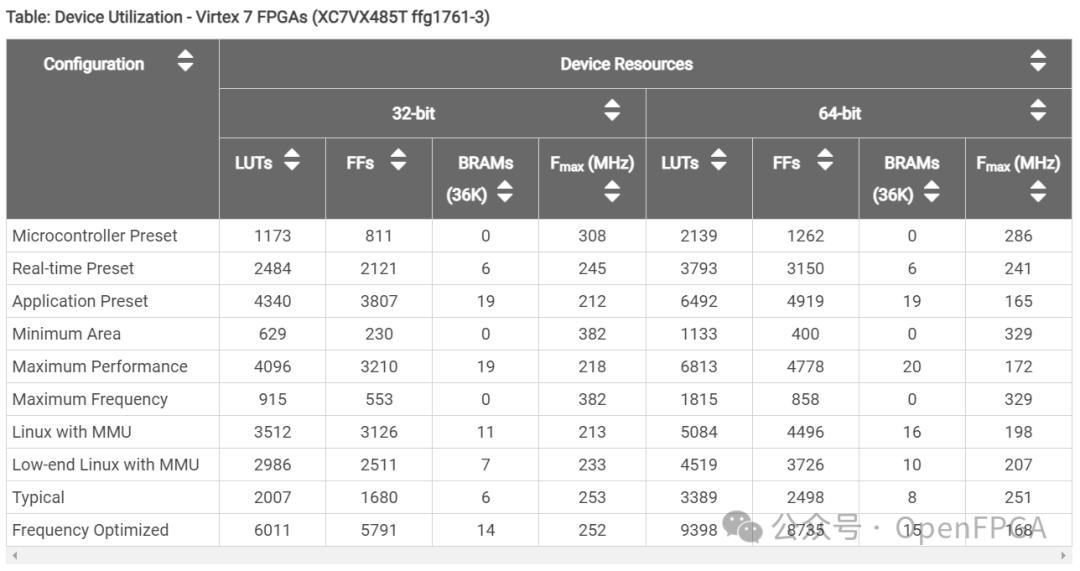

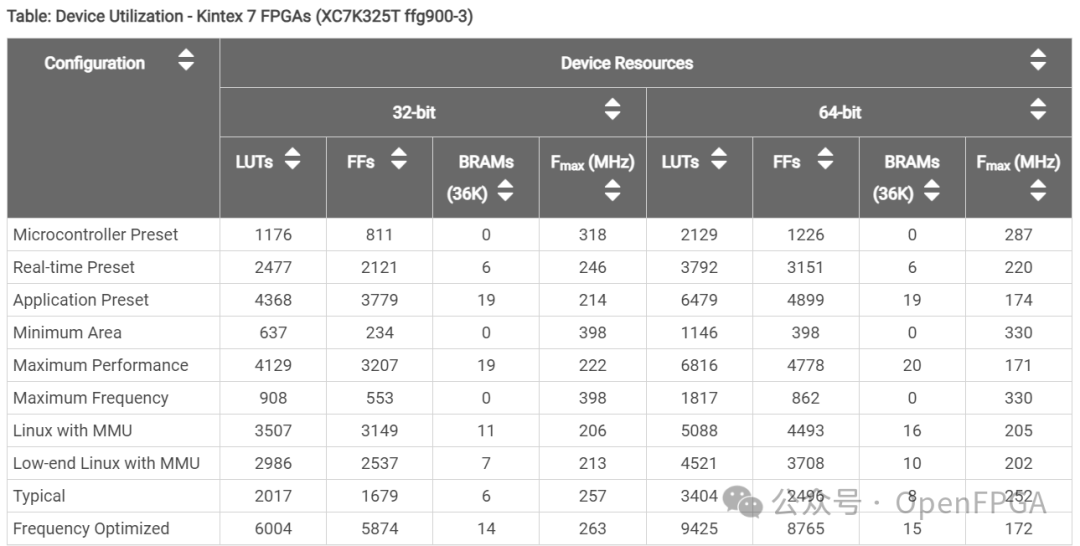

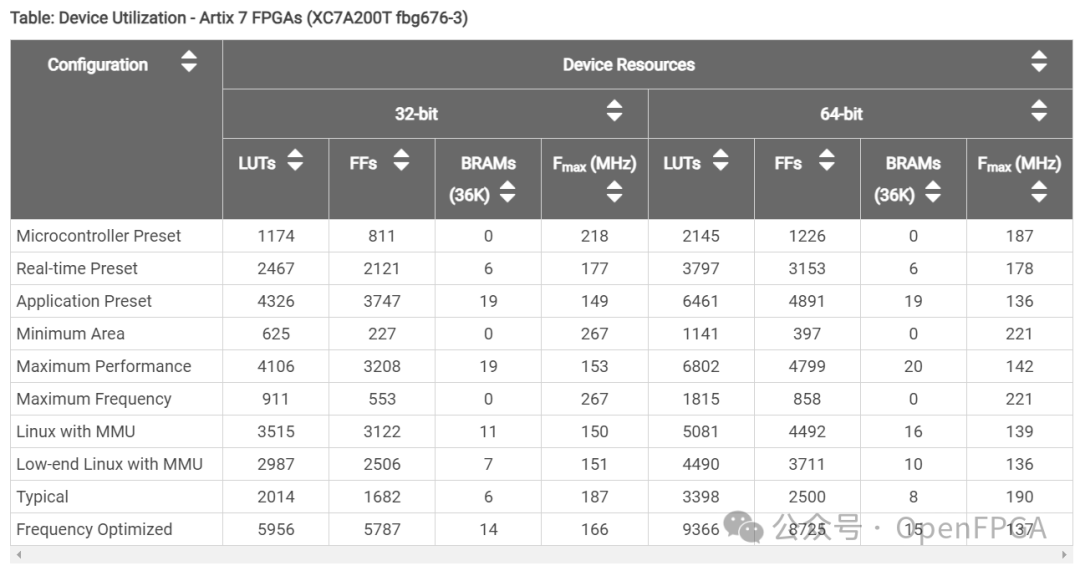

作为对比,看下microblaze原版本资源情况:

示例架构

32 位处理器内核 (RV32IMAFC)

JTAG 调试接口

紧密耦合的本地存储器

SPI 控制器

I2C 控制器

UART

中断控制器

定时器

GPIO

总结

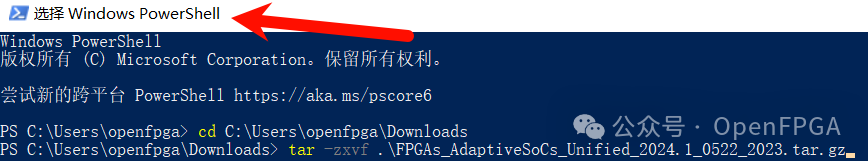

下载完整安装包后,windows用户可以直接使用powershell,输入以下指令进行解压:

tar -zxvf .\安装包路径

license通用

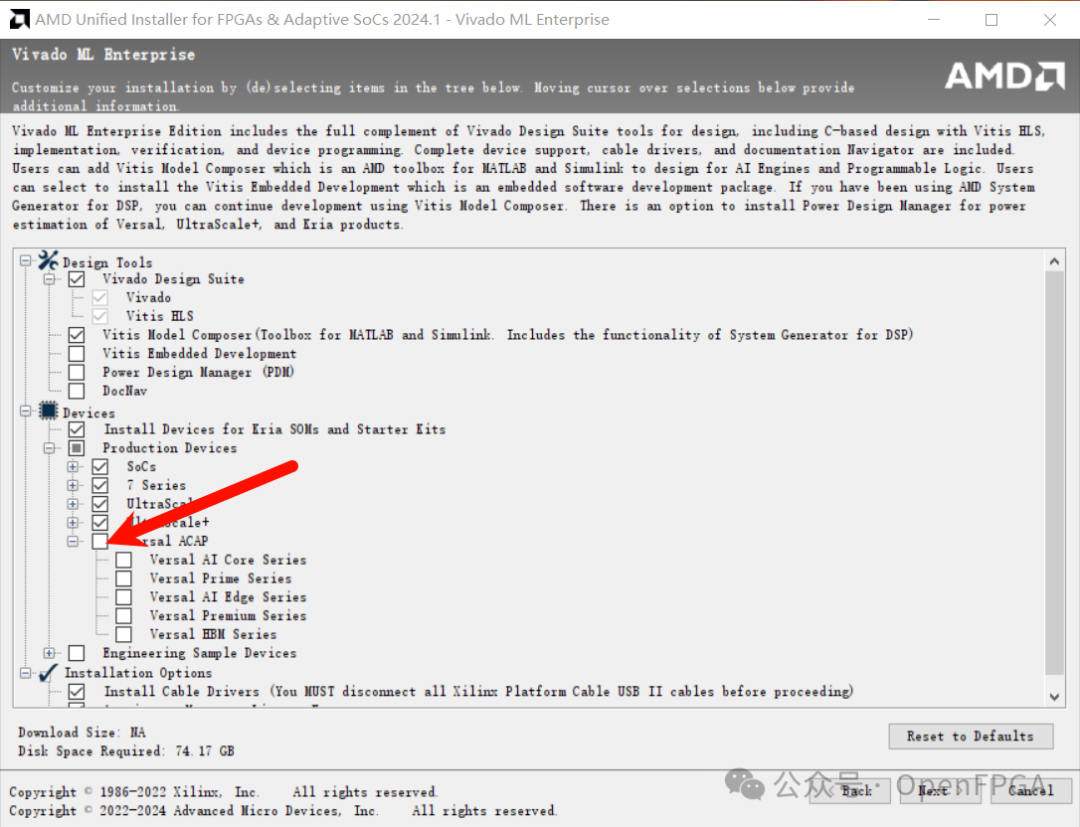

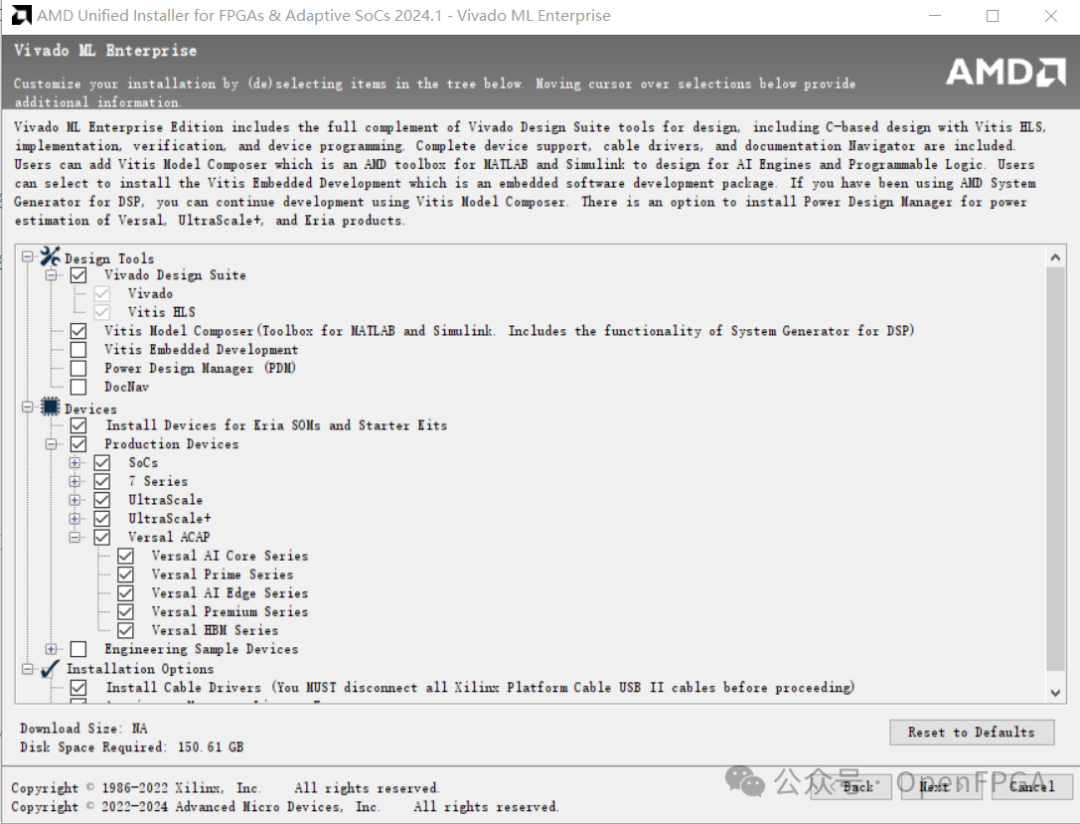

安装时勾选ACAP组件,多一倍的空间

最新的软核免费

下载链接

链接:

https://pan.baidu.com/s/16ZWBA-J8iiIraDM6gQvtmQ?pwd=open

微信公众号

微信公众号

评论记录:

回复评论: