Makefile中的include语句是把被包含的文件的内容包含当前文件中,类似于C语言中的include关键词。

但是使用时要特别注意避免陷入无限循环的死循环中。

来看下面这个有问题的例子:

顶层目录有文件Makefile和文件Makefile.build,

文件Makefile的内容如下:

str1 := MyNameIsSuWenhao

TOPDIR := $(shell pwd)

all:

make -C ./ -f $(TOPDIR)/Makefile.build

- 1

- 2

- 3

- 4

- 5

- 6

文件Makefile.build的内容如下:

include Makefile

# 打印str1的值

myprint:

@echo "str1's value is: $(str1)"

- 1

- 2

- 3

- 4

- 5

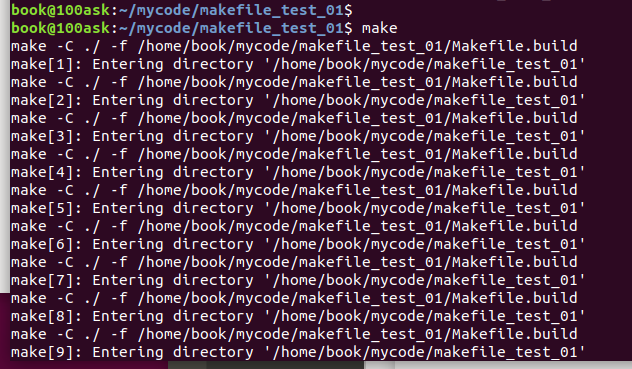

运行命令:make时,我本意是想打印出变量str1的内容,但是构建程序会一直循环输出下面两条信息:

make[484]: Entering directory '/home/book/mycode/makefile_test_01'

make -C ./ -f /home/book/mycode/makefile_test_01/Makefile.build

.....

- 1

- 2

- 3

这是什么原因呢?

原因在于Makefile.build中的include命令会把Makefile中的所有内容包含进来,相当于Makefile.build的内容如下:

str1 := MyNameIsSuWenhao

TOPDIR := $(shell pwd)

all:

make -C ./ -f $(TOPDIR)/Makefile.build

# 打印str1的值

myprint:

@echo "str1's value is: $(str1)"

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

我们看此时Makefile.build的第一个目标是all目标,所以Makefile.build会去执行这个all目标,这个all目标的命令部分为:make -C ./ -f $(TOPDIR)/Makefile.build,也就是说又去调用文件$(TOPDIR)/Makefile.build进行构建,而一旦调用文件$(TOPDIR)/Makefile.build,它就又会去调用文件$(TOPDIR)/Makefile.build,这样就陷入了一种无限循环中。

怎么解决这个问题呢?

这里我们是想让Makefile.build去执行目标myprint,我们引入Makefile文件是为了使用它里面定义的那些变量及其值,而不是让Makefile.build去执行目标all,解决的方法很简单也很巧妙,我们只需要在Makefile.build中位于include命令前定义一个内容为空的目标myprint即可,比如下面的代码:

myprint:

include Makefile

# 打印str1的值

myprint:

@echo "str1's value is: $(str1)"

- 1

- 2

- 3

- 4

- 5

- 6

- 7

这个代码中,第一行就是我们想在Makefile.build中执行的目标myprint,根据Makefile的规则,Makefile会先解析内容,再执行,当它解析时,发现后面还有个同名的目标myprint,再根据Makefile的规则,当有同名目标时,后面的覆盖前面的,所以它会去执行后面的目标myprint,这样就跳过了因为include包含进来的all目标。

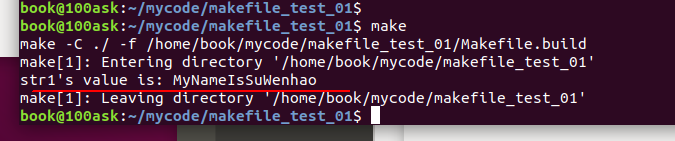

运行效果如下:

QQ群名片

QQ群名片

评论记录:

回复评论: